- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67320 > 5962-0053001HXC DUAL 1-CH 12-BIT PROPRIETARY METHOD ADC, SERIAL ACCESS, CQFP68 PDF資料下載

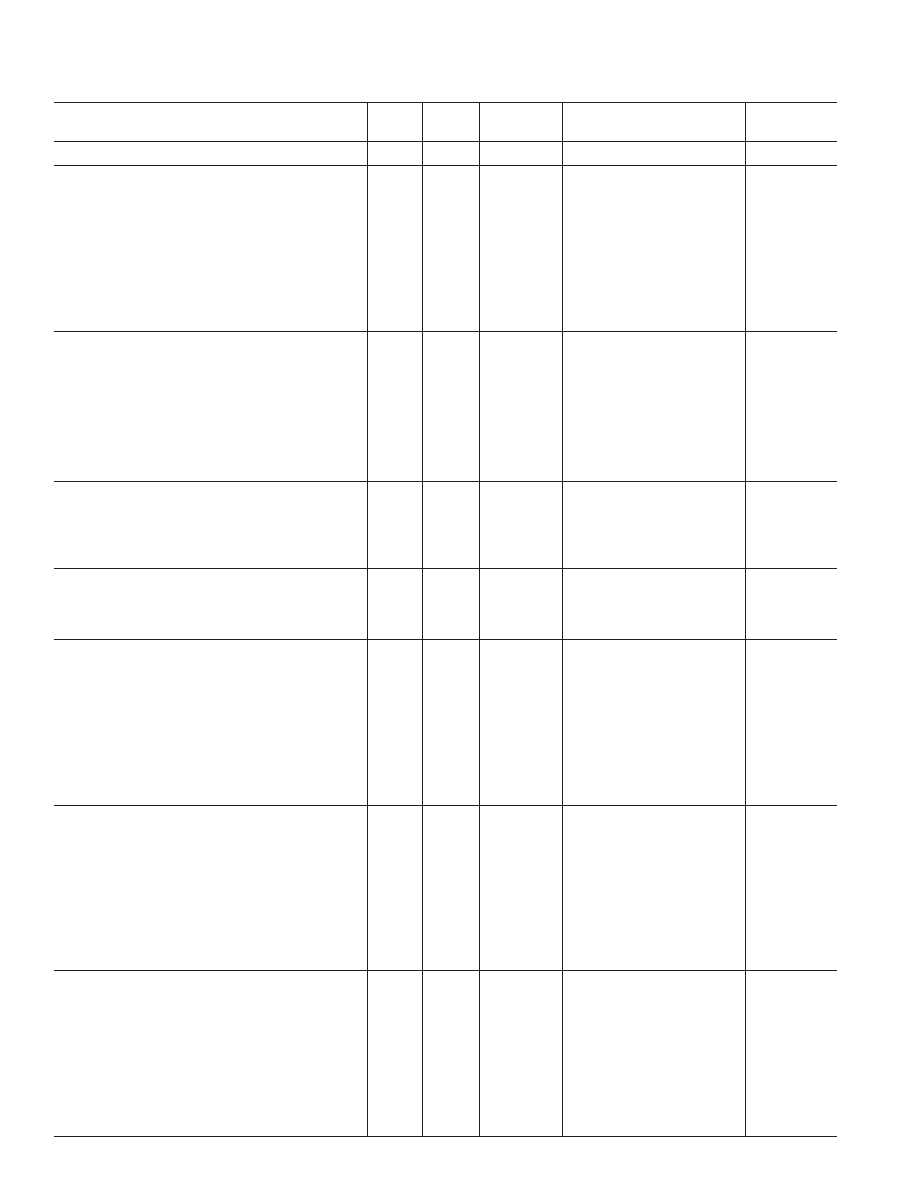

參數(shù)資料

| 型號: | 5962-0053001HXC |

| 元件分類: | ADC |

| 英文描述: | DUAL 1-CH 12-BIT PROPRIETARY METHOD ADC, SERIAL ACCESS, CQFP68 |

| 封裝: | CERAMIC, LCC-68 |

| 文件頁數(shù): | 12/20頁 |

| 文件大小: | 4809K |

| 代理商: | 5962-0053001HXC |

REV. A

–2–

AD13280–SPECIFICATIONS

(AVCC = +5 V, AVEE = –5 V, DVCC = +3.3 V; applies to each ADC with Front-End

Amplifier, unless otherwise noted.)

Test

Mil

AD13280AZ/BZ

Parameter

Temp

Level

Subgroup

Min

Typ

Max

Unit

RESOLUTION

12

Bits

DC ACCURACY

1

No Missing Codes

Full

IV

12

Guaranteed

Offset Error

25

°CI

1

–2.2

±1.0

+2.2

% FS

Full

VI

2, 3

–2.2

±1.0

+2.2

% FS

Offset Error Channel Match

Full

VI

1, 2, 3

–1.0

±0.1

+1.0

%

Gain Error

2

25

°CI

1

–3

–1.0

+1

% FS

Full

VI

2, 3

–5.0

±2.0

+5.0

% FS

Gain Error Channel Match

25

°CI

1

–1.5

±0.5

+1.5

%

Max

VI

2

–3.0

±1.0

+3.0

%

Min

VI

3

–5

±1.0

+5

%

SINGLE-ENDED ANALOG INPUT

Input Voltage Range

AMP-IN-X-1

Full

V

±0.5

V

AMP-IN-X-2

Full

V

±1.0

V

Input Resistance

AMP-IN-X-1

Full

IV

12

99

100

101

AMP-IN-X-2

Full

IV

12

198

200

202

Capacitance

25

°CV

4.0

7.0

pF

Analog Input Bandwidth

3

Full

V

100

MHz

DIFFERENTIAL ANALOG INPUT

Analog Signal Input Range

A+IN to A–IN and B+IN to B–IN

4

Full

V

±1V

Input Impedance

25

°CV

618

Analog Input Bandwidth

Full

V

50

MHz

ENCODE INPUT (ENC, ENC)

1

Differential Input Voltage

Full

IV

12

0.4

V p-p

Differential Input Resistance

25

°CV

10

k

Differential Input Capacitance

25

°CV

2.5

pF

SWITCHING PERFORMANCE

Maximum Conversion Rate

5

Full

VI

4, 5, 6

80

MSPS

Minimum Conversion Rate

5

Full

IV

12

20

MSPS

Aperture Delay (tA)25

°CV

1.5

ns

Aperture Delay Matching

25

°CIV

12

250

500

ps

Aperture Uncertainty (Jitter)

25

°CV

0.3

ps rms

ENCODE Pulsewidth High at Max Conversion Rate

25

°CIV12

4.75

6.25

8

ns

ENCODE Pulsewidth Low at Max Conversion Rate

25

°CIV12

4.75

6.25

8

ns

Output Delay (tOD)

Full

V

5

ns

Encode, Rising to Data Ready, Rising Delay

Full

V

8.5

ns

SNR

1, 6

Analog Input @ 10 MHz

25

°CI

4

66.5

70

dBFS

Min

II

6

64.5

dBFS

Max

II

5

66.3

dBFS

Analog Input @ 21 MHz

25

°CI

4

66.5

70

dBFS

Min

II

6

64

dBFS

Max

II

5

66.3

dBFS

Analog Input @ 37 MHz

25

°CI

46365

dBFS

Min

II

6

61.5

dBFS

Max

II

5

63

dBFS

SINAD

1, 7

Analog Input @ 10 MHz

25

°CI

46669

dBFS

Min

II

6

63.5

dBFS

Max

II

5

66

dBFS

Analog Input @ 21 MHz

25

°CI

464

68.5

dBFS

Min

II

6

63

dBFS

Max

II

5

64

dBFS

Analog Input @ 37 MHz

25

°CI

45459

dBFS

Min

II

6

53

dBFS

Max

II

5

54

dBFS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5962-005300HXA | DUAL 1-CH 12-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| 5962-005300HXX | DUAL 1-CH 12-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| 5962-0150601HXX | DUAL 1-CH 14-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| 5962-0251002HXC | 1-OUTPUT 8 W DC-DC REG PWR SUPPLY MODULE |

| 5962-9213902HZC | 1-OUTPUT 12 W DC-DC REG PWR SUPPLY MODULE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 5962005304899 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 5962005308115 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 5962005345643 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 5962-0053901QYA | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSOR |

| 5962-0053901QYC | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSOR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。