- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371400 > 24WC128 64K 8K x 8 Battery-Voltage CMOS E2PROM PDF資料下載

參數(shù)資料

| 型號: | 24WC128 |

| 元件分類: | EEPROM |

| 英文描述: | 64K 8K x 8 Battery-Voltage CMOS E2PROM |

| 中文描述: | 64K的8K的× 8電池電壓的CMOS E2PROM的 |

| 文件頁數(shù): | 5/8頁 |

| 文件大小: | 43K |

| 代理商: | 24WC128 |

Preliminary

CAT24WC128

5

Doc. No. 25060-00 6/99 S-1

1

0

1

0

A2

A1

A0

R/W

DEVICE ADDRESSING

The bus Master begins a transmission by sending a

START condition. The Master sends the address of the

particular slave device it is requesting. The seven most

significant bits of the 8-bit slave address are fixed as

1010XXX (Fig. 5), where X can be a 0 or 1. The last bit

of the slave address specifies whether a Read or Write

operation is to be performed. When this bit is set to 1, a

Read operation is selected, and when set to 0, a Write

operation is selected.

After the Master sends a START condition and the slave

address byte, the CAT24WC128 monitors the bus and

responds with an acknowledge (on the SDA line) when

its address matches the transmitted slave address. The

CAT24WC128 then performs a Read or Write operation

depending on the state of the R/

W

bit.

Acknowledge

After a successful data transfer, each receiving device is

required to generate an acknowledge. The Acknowledg-

ing device pulls down the SDA line during the ninth clock

cycle, signaling that it received the 8 bits of data.

The CAT24WC128 responds with an acknowledge after

receiving a START condition and its slave address. If the

device has been selected along with a write operation,

it responds with an acknowledge after receiving each 8-

bit byte.

When the CAT24WC128 begins a READ mode it trans-

mits 8 bits of data, releases the SDA line, and monitors

the line for an acknowledge. Once it receives this ac-

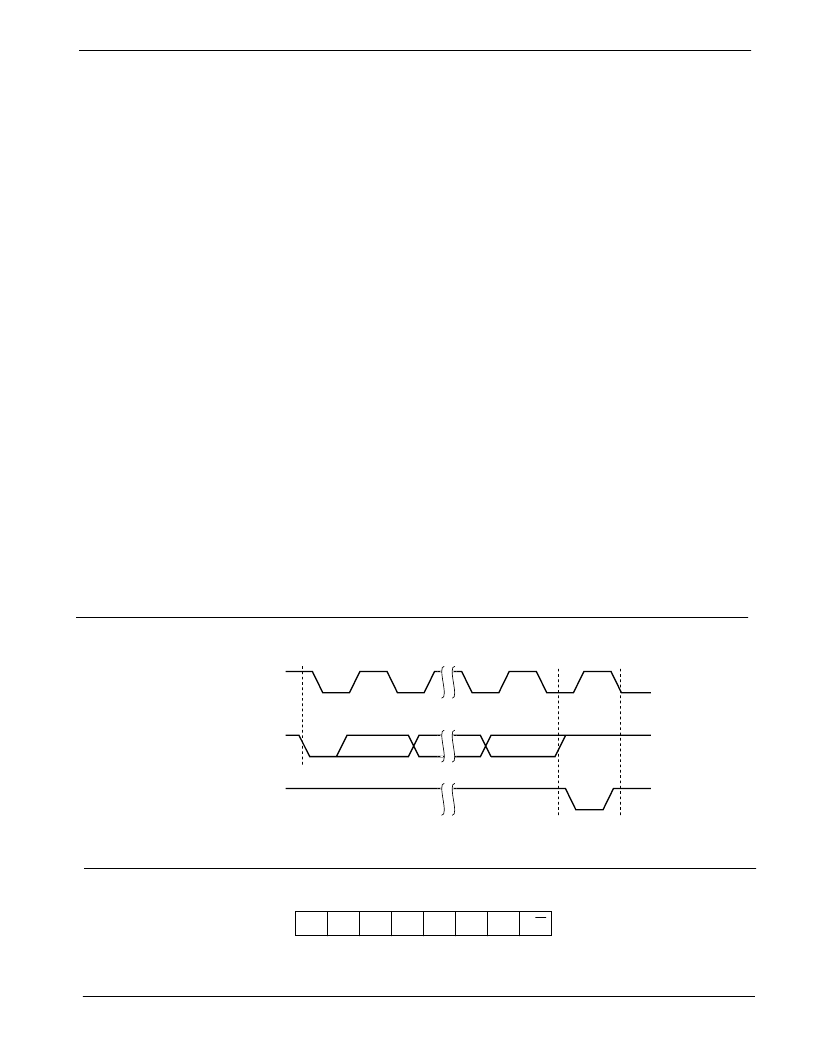

Figure 4. Acknowledge Timing

5027 FHD F07

Figure 5. Slave Address Bits

5020 FHD F06

ACKNOWLEDGE

1

START

SCL FROM

MASTER

8

9

DATA OUTPUT

FROM TRANSMITTER

DATA OUTPUT

FROM RECEIVER

knowledge, the CAT24WC128 will continue to transmit

data. If no acknowledge is sent by the Master, the device

terminates data transmission and waits for a STOP

condition.

WRITE OPERATIONS

Byte Write

In the Byte Write mode, the Master device sends the

START condition and the slave address information

(with the R/

W

bit set to zero) to the Slave device. After

the Slave generates an acknowledge, the Master sends

two 8-bit address words that are to be written into the

address pointers of the CAT24WC128. After receiving

another acknowledge from the Slave, the Master device

transmits the data to be written into the addressed

memory location. The CAT24WC128 acknowledges

once more and the Master generates the STOP condi-

tion. At this time, the device begins an internal program-

ming cycle to nonvolatile memory. While the cycle is in

progress, the device will not respond to any request from

the Master device.

Page Write

The CAT24WC128 writes up to 64 bytes of data, in a

single write cycle, using the Page Write operation. The

page write operation is initiated in the same manner as

the byte write operation, however instead of terminating

after the initial byte is transmitted, the Master is allowed

to send up to 63 additional bytes. After each byte has

been transmitted, CAT24WC128 will respond with an

X is Don't Care, can be a '0' or a '1'.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 24WC32 | 64K 8K x 8 Battery-Voltage CMOS E2PROM |

| 250-8501-010 | Low-Power, SPST, Fast, CMOS Analog Switch |

| 2500-10J | Molded Unshielded RF Coils |

| 2500-00J | Molded Unshielded RF Coils |

| 2500-02J | Molded Unshielded RF Coils |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 24WC16 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:1K/2K/4K/8K/16K-Bit Serial E2PROM |

| 24WC256KI | 制造商:CSI 功能描述: |

| 24WC32 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:32K/64K-Bit I2C Serial CMOS E2PROM |

| 24WC32P | 制造商:CATALYST 功能描述: |

| 24WR10KLFTR | 制造商:BITECH 制造商全稱:Bi technologies 功能描述:4mm Diameter Single Turn Cermet Trimming Potentiometer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。