- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372985 > ZPSD511B1-90LI Field-Programmable Peripheral PDF資料下載

參數(shù)資料

| 型號(hào): | ZPSD511B1-90LI |

| 英文描述: | Field-Programmable Peripheral |

| 中文描述: | 現(xiàn)場(chǎng)可編程外圍 |

| 文件頁數(shù): | 63/153頁 |

| 文件大?。?/td> | 1036K |

| 代理商: | ZPSD511B1-90LI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁當(dāng)前第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁

PSD5XX Famly

60

APDENBit

ALE Power

Down Polarity

X

ALE Status

APDCounter

0

X

Not Counting

1

X

Pulsing

Not Counting

Counting (Activates Standby

Mode After 15 Clocks)

Counting (Activates Standby

Mode After 15 Clocks)

1

1

1

1

0

0

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

TMR CLK

ZPLD

RCLK

ZPLD

ACLK

ZPLD

TURBO

APD

ENABLE

ALE PD

Polarity

*

CMISER

1 = OFF

1 = OFF

1 = OFF

1 = OFF

1 = ON

1 = ON

1 = HIGH

PMMR0

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

*

*

*

*

*

*

Sleep

Mode

APD CLK

1 = ON

1 = CLKIN

PMMR1

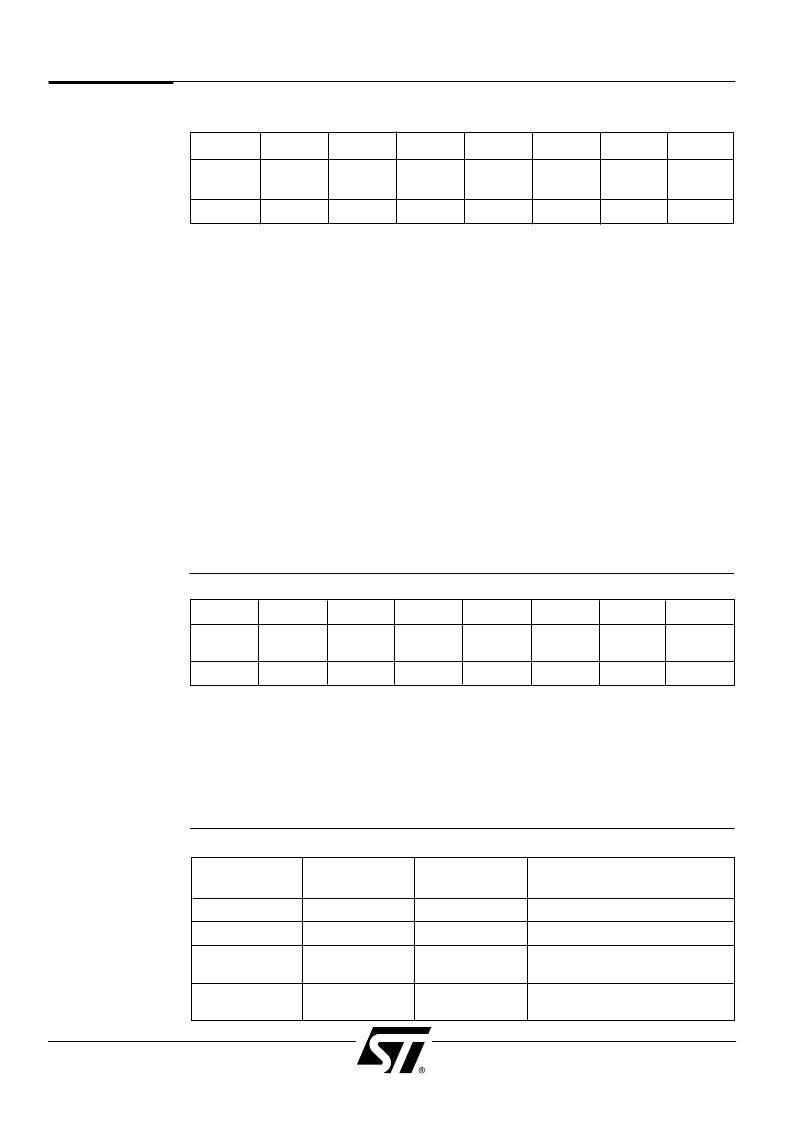

Table 17. Power Management Mode Registers (PMMR0, PMMR1)

Table 18. APDCounter Operation

Power

Management

Unit

(Cont.)

Bit 0

*

= Should be set to High (1) to operate the APD.

Bit 1

0 = ALE Power Down (PD) Polarity Low.

1 = ALE Power Down (PD) Polarity High.

Bit 2

0 = Automatic Power Down (APD) Disable.

1 = Automatic Power Down (APD) Enable.

Bit 3

0 = EPROM/SRAM CMiser is OFF.

1 = EPROM/SRAM CMiser is ON.

Bit 4

0 = ZPLD Turbo is ON. ZPLD is always ON.

1 = ZPLD Turbo is OFF. ZPLD will Power Down when inputs are not changing.

Bit 5

0 = ZPLD Clock Input into the Array from the CLKIN pin input is connected. Every

Clock change will Power Up the ZPLD when Turbo bit is OFF.

1 = ZPLD Clock Input into the Array from the CLKIN pin input is disconnected.

Bit 6

0 = ZPLD Clock Input into the the MacroCell registers from the CLKIN pin input

is connected.

1 = ZPLD Clock Input into the the MacroCell registers from the CLKIN pin input

is disconnected.

Bit 7

0 = In the PSD5XX Clock Input is connected to the Timer.

1 = In the PSD5XX Clock Input is disconnected from the Timer.

Bit 0

0 = Automatic Power Down Unit Clock is connected to Port E7 (PE7) alternate

function input.

1 = Automatic Power Down Unit Clock is connected to the PSD Clock

input (CLKIN).

0 = Sleep Mode Disabled.

1 = Sleep Mode Enabled.

Bit 2–7

0 = Reserved for future use, should be set to zero.

Bit 1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZPSD512B1-12UI | Field-Programmable Peripheral |

| ZPSD512B1-15J | Field-Programmable Peripheral |

| ZPSD512B1-15JI | Field-Programmable Peripheral |

| ZPSD512B1-15LI | Schottky Barrier Diodes |

| ZPSD512B1-15LM | Field-Programmable Peripheral |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZPSD512B1-C-90UI | 制造商:WSI 功能描述: |

| ZPSD513B1-C-15L | 制造商:WSI 功能描述: |

| ZPSD602E1-15L | 制造商:WSI 功能描述: |

| ZPSD611E1-15J | 制造商:WSI 功能描述: |

| ZPSD611E1-15JI | 制造商:WSI 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。