- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372985 > ZPSD511B1-90LI Field-Programmable Peripheral PDF資料下載

參數(shù)資料

| 型號: | ZPSD511B1-90LI |

| 英文描述: | Field-Programmable Peripheral |

| 中文描述: | 現(xiàn)場可編程外圍 |

| 文件頁數(shù): | 4/153頁 |

| 文件大小: | 1036K |

| 代理商: | ZPSD511B1-90LI |

第1頁第2頁第3頁當(dāng)前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁

1

1.0

Introduction

Programmable Peripheral

PSD5XX Famly

Field-Programmable Microcontroller Peripherals

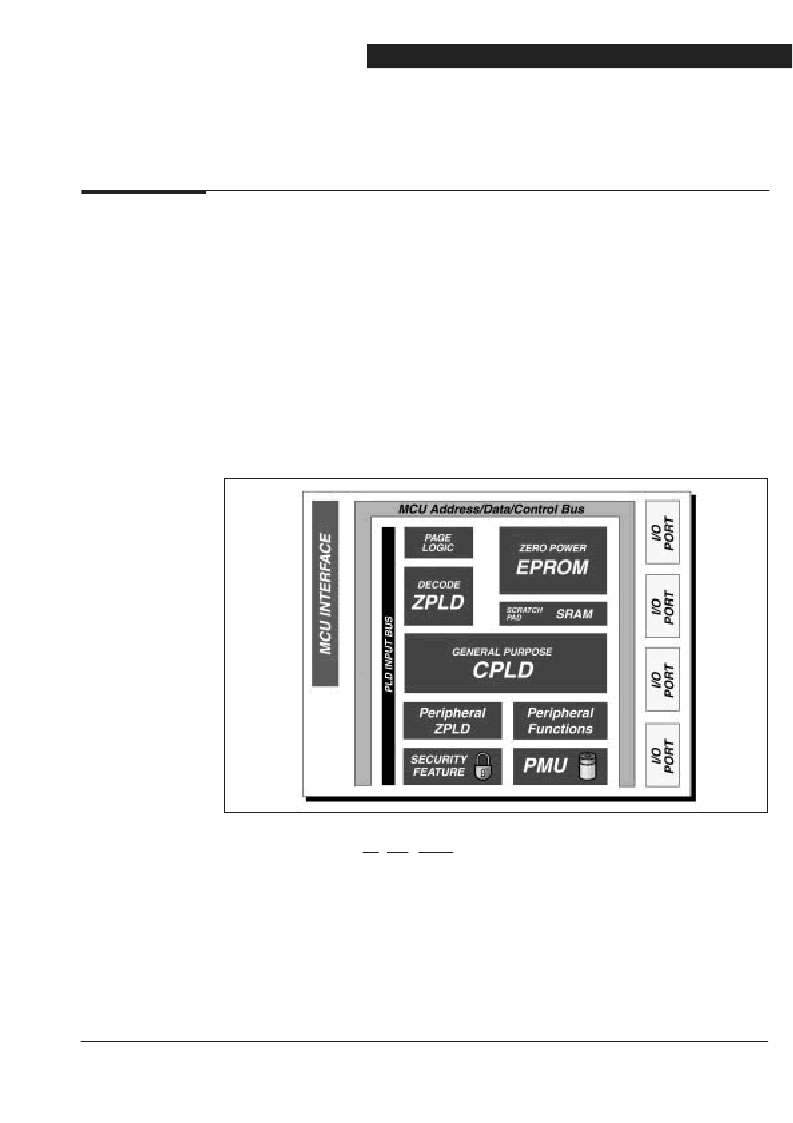

The PSD5XX family is a microcontroller peripheral that integrates high-performance and

user-configurable blocks of EPROM, programmable logic, and SRAM into one part. The

PSD5XX is also loaded with a variety of features, such as Counter/Timers, Interrupt

controller, power management, and page logic. The PSD5XX products also provide a

powerful microcontroller interface that eliminates the need for external “glue logic”. The no

“glue logic” concept provides a user-programmable interface to a variety of 8- and 16-bit

(multiplexed or non-multiplexed) microcontrollers that is easy to use. The part’s integration,

small form factor, low power consumption, and ease of use make it the ideal part for

interfacing to virtually any microcontroller.

The PSD5XX provides three Zero-power PLDs (ZPLDs): a Decode PLD (DPLD), a

General-purpose PLD (PLD), and a Peripheral PLD (PPLD). The ZPLDs have a total of 61

inputs, 140 product terms, 30 macrocells, and 24 I/O connections. A configuration bit

(Turbo) can be set by the MCU, and will automatically place the ZPLDs into standby if

no inputs are changing. The ZPLDs are designed to consume minimum power using Zero

Power CMOS technology that uses low standby current. Unused product terms are

automatically disabled, also reducing power, regardless of the Turbo bit setting.

The main function of the DPLD is to perform address decoding for the internal I/O ports,

EPROM, and SRAM. The address decoding can be based on up to 24 bits of address

inputs, control signals (RD, WR, PSEN, etc.), and internal page logic. The DPLD supports

separate program and data spaces (for 8031 compatible MCUs).

The General-purpose PLD (GPLD) can be used to implement various logic defined by the

user, such as:

State machines

Loadable counters and shift registers

Inter-processor mailbox

External control logic (chip selects, output enables, etc.).

The GPLD has access to up to 61 inputs, 118 product terms, 24 macrocells, and 24 I/O

pins.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZPSD512B1-12UI | Field-Programmable Peripheral |

| ZPSD512B1-15J | Field-Programmable Peripheral |

| ZPSD512B1-15JI | Field-Programmable Peripheral |

| ZPSD512B1-15LI | Schottky Barrier Diodes |

| ZPSD512B1-15LM | Field-Programmable Peripheral |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZPSD512B1-C-90UI | 制造商:WSI 功能描述: |

| ZPSD513B1-C-15L | 制造商:WSI 功能描述: |

| ZPSD602E1-15L | 制造商:WSI 功能描述: |

| ZPSD611E1-15J | 制造商:WSI 功能描述: |

| ZPSD611E1-15JI | 制造商:WSI 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。