- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372985 > ZPSD502B1-12UI Field-Programmable Peripheral PDF資料下載

參數(shù)資料

| 型號: | ZPSD502B1-12UI |

| 英文描述: | Field-Programmable Peripheral |

| 中文描述: | 現(xiàn)場可編程外圍 |

| 文件頁數(shù): | 82/153頁 |

| 文件大小: | 1036K |

| 代理商: | ZPSD502B1-12UI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁當前第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁

PSD5XX Famly

79

DLCY

Scale Bit

DIV

0

1

2

3

4

5

6

7

8

9

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

DLCY

Scale Bit

DIV

1

2

3

4

5

6

7

8

9

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

40

48

56

64

72

80

88

96

104

112

120

128

136

144

152

160

168

176

184

192

200

208

216

224

232

240

248

256

264

272

280

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

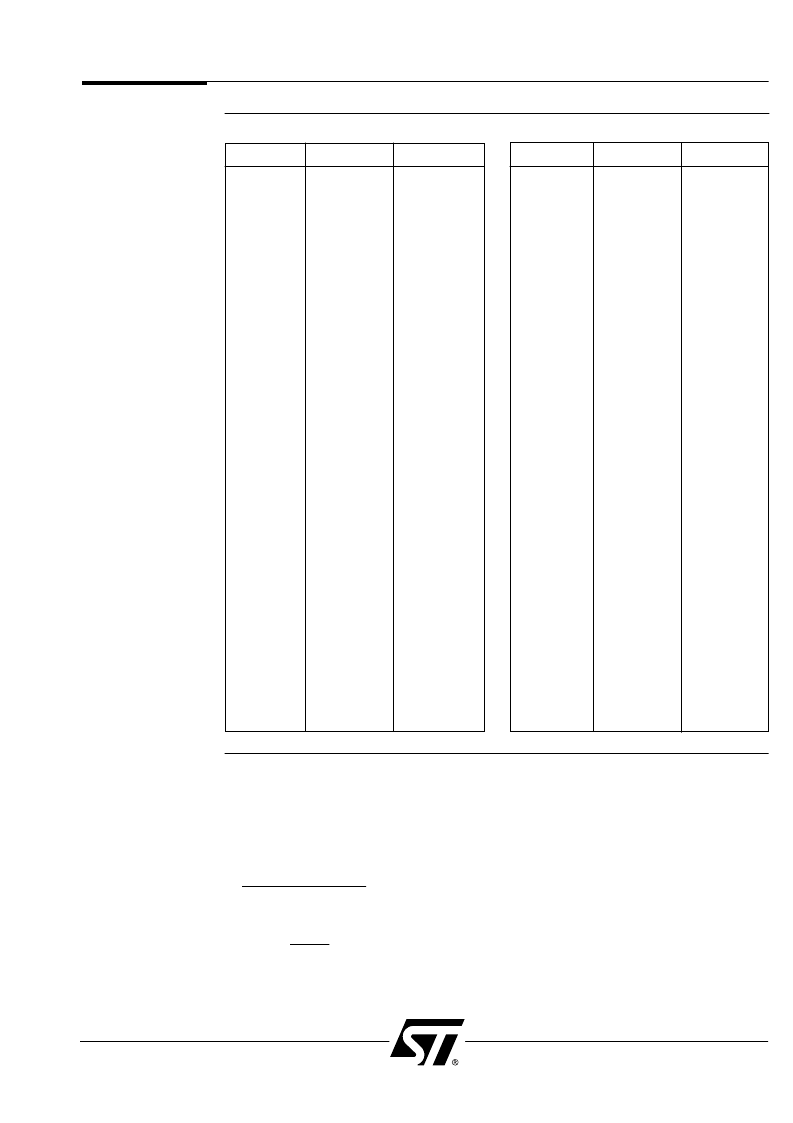

Table 22. DLCY, Scale Bit and DIV to Generate Dfferent Clock Dvisions

Sample Calculation of Timer Input Clock

External input clock to the PSD5XX is 8 MHz.

If required Counter/Timers 0 – 3 count frequency is 1 MHz then

The Counter/Timer CLOCK Input

(External Clock input)

=

(DIV)

8 MHz

(DIV)

1 MHz =

=

>

(DIV) = 8

Therefore from Table 22 when (DIV) = 8, the Scale-Bit in the “Global Command Register” is

set to a 0 and the DLCY register to a value of 4.

Counter/Timer

Operation

(Cont.)

Counter/Timer Clock Input

(Cont.)

相關PDF資料 |

PDF描述 |

|---|---|

| ZPSD502B1-15J | Avalanche Glass Passivated Bridge Rectifiers |

| ZPSD502B1-15JI | Avalanche Glass Passivated Bridge Rectifiers |

| ZPSD502B1-15LI | Avalanche Glass Passivated Bridge Rectifiers |

| ZPSD502B1-15LM | Avalanche Glass Passivated Bridge Rectifiers |

| ZPSD502B1-15U | Avalanche Glass Passivated Bridge Rectifiers |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ZPSD503B1-C-15L | 制造商:WSI 功能描述: |

| ZPSD512B1-C-90UI | 制造商:WSI 功能描述: |

| ZPSD513B1-C-15L | 制造商:WSI 功能描述: |

| ZPSD602E1-15L | 制造商:WSI 功能描述: |

| ZPSD611E1-15J | 制造商:WSI 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。