- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373783 > ZL30105QDG (ZARLINK SEMICONDUCTOR INC) Digital Clamp-On Meter; DMM Type:Clamp; No. of Digits/Alpha:3-3/4; DMM Response Type:True RMS; Calibrated:No; Current Setting AC:1000A; Resistance Measuring Range:400 Ohm to 10 MOhm; Voltage Measuring Range AC:600V RoHS Compliant: NA PDF資料下載

參數(shù)資料

| 型號: | ZL30105QDG |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | Digital Clamp-On Meter; DMM Type:Clamp; No. of Digits/Alpha:3-3/4; DMM Response Type:True RMS; Calibrated:No; Current Setting AC:1000A; Resistance Measuring Range:400 Ohm to 10 MOhm; Voltage Measuring Range AC:600V RoHS Compliant: NA |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP64 |

| 封裝: | 10 X 10 MM, 1 MM HEIGHT, MS-026ACD, TQFP-64 |

| 文件頁數(shù): | 16/50頁 |

| 文件大小: | 691K |

| 代理商: | ZL30105QDG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁

ZL30105

Data Sheet

16

Zarlink Semiconductor Inc.

where:

-

0.01 ppm is the accuracy of the Holdover mode

-

0 ns is the maximum phase discontinuity in the transition from the Normal mode to the Holdover mode

-

13 ns is the maximum phase discontinuity in the transition from the Holdover mode to the Normal mode

when a new TIE corrector value is calculated

HMS=0

: When the same ten Normal to Holdover to Normal mode changes occur and in each case Holdover mode

was entered for 2 seconds, then the overall MTIE would be 20 ns. As the delay value for the TIE corrector circuit is

not updated, there is no 13 ns measurement error at this point. The phase can still drift for 20 ns when the PLL is in

Holdover mode but when the PLL enters Normal mode again, the phase moves back to the original point so the

phase is not accumulated.

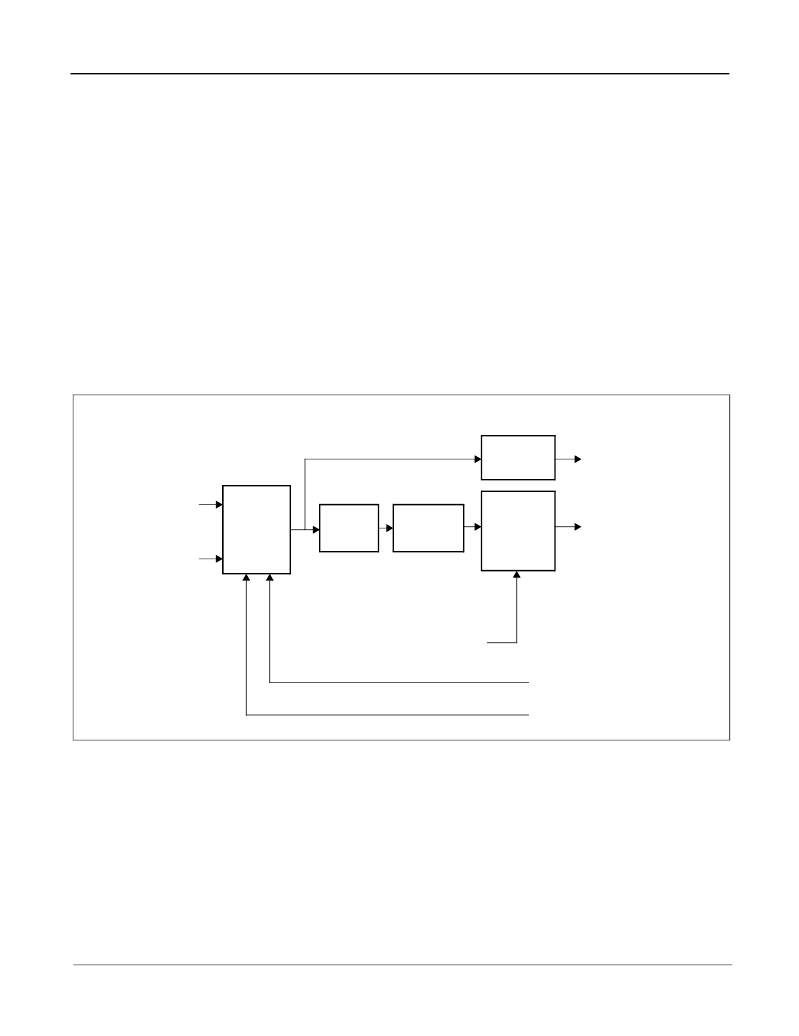

2.4 Digital Phase Lock Loop (DPLL)

The DPLL of the ZL30105 consists of a phase detector, a limiter, a loop filter and a digitally controlled oscillator as

shown in Figure 11. The data path from the phase detector to the limiter is tapped and routed to the lock indicator

that provides a lock indication which is output at the LOCK pin.

Figure 11 - DPLL Block Diagram

Phase Detector

- the phase detector compares the virtual reference signal from the TIE corrector circuit with the

feedback signal and provides an error signal corresponding to the phase difference between the two. This error

signal is passed to the limiter circuit.

Limiter

- the limiter receives the error signal from the phase detector and ensures that the DPLL responds to all

input transient conditions with a maximum output phase slope compliant with the applicable standards. The phase

slope limit is dependent on the APP_SEL1:0 and SEC_MSTR pins and is listed in Table 2.

Loop Filter

- the loop filter is similar to a first order low pass filter with a bandwidth of 1.8 Hz or 3.6 Hz, suitable to

provide Primary Master timing. When Secondary Master mode is selected (SEC_MSTR=1), the filter bandwidth is

set to 922 Hz. For stability reasons, the loop filter bandwidth for 2 kHz and 8 kHz reference inputs is limited to a

maximum of 14 Hz and 58 Hz respectively.

State Select from

Control State Machine

Feedback signal from

Frequency Select MUX

DPLL Reference to

Frequency Synthesizer

Virtual Reference

from

TIE Corrector Circuit

Limiter

Loop Filter

Digitally

Controlled

Oscillator

Phase

Detector

REF2_SYNC

frame pulse

Lock

Detector

LOCK

feedback frame pulse; F8o or F2ko

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL30106QDG1 | SONET/SDH/PDH Network Interface DPLL |

| ZL30106 | SONET/SDH/PDH Network Interface DPLL |

| ZL30106QDG | SONET/SDH/PDH Network Interface DPLL |

| ZL30107 | GbE Line Card Synchronizer |

| ZL30107GGG | GbE Line Card Synchronizer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL30105QDG1 | 制造商:Microsemi Corporation 功能描述:CLOCK SYNTHESIZER 64TQFP - Trays 制造商:Microsemi Corporation 功能描述:IC Pb Free T1/E1 System Synchronizer 制造商:Zarlink Semiconductor Inc 功能描述:CLOCK SYNTHESIZER 64TQFP - Trays 制造商:Zarlink Semiconductor Inc 功能描述:IC Pb Free T1/E1 System Synchronizer |

| ZL30106 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:SONET/SDH/PDH Network Interface DPLL |

| ZL30106_05 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:SONET/SDH/PDH Network Interface DPLL |

| ZL30106QDG | 制造商:Zarlink Semiconductor Inc 功能描述:SONET/SDH/PDH NETWORK INTRFC 64TQFP - Trays 制造商:Microsemi 功能描述:Microsemi ZL30106QDG Communication Misc |

| ZL30106QDG1 | 制造商:Zarlink Semiconductor Inc 功能描述:SONET/SDH/PDH NETWORK INTRFC 64TQFP - Trays 制造商:Zarlink Semiconductor Inc 功能描述:PB FREE SONET/SDH/PDH NTWK INTERFACEDPLL |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。