- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373782 > ZL10313QCG1 (ZARLINK SEMICONDUCTOR INC) Augumented Cat. 6 T568A/B Modular Jack; No. of Ports:48; Mounting Type:2U Panel; Approval Categories:Augmented Category 6; Jacks FCC part 68, Subpart F & IEC-603-7 compliant RoHS Compliant: Yes PDF資料下載

參數(shù)資料

| 型號(hào): | ZL10313QCG1 |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | Augumented Cat. 6 T568A/B Modular Jack; No. of Ports:48; Mounting Type:2U Panel; Approval Categories:Augmented Category 6; Jacks FCC part 68, Subpart F & IEC-603-7 compliant RoHS Compliant: Yes |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| 封裝: | 7 X 7 MM, 1.40 MM HEIGHT, LEAD FREE, MS-026BBD, LQFP-64 |

| 文件頁數(shù): | 22/26頁 |

| 文件大?。?/td> | 450K |

| 代理商: | ZL10313QCG1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁

ZL10313

Data Sheet

22

Zarlink Semiconductor Inc.

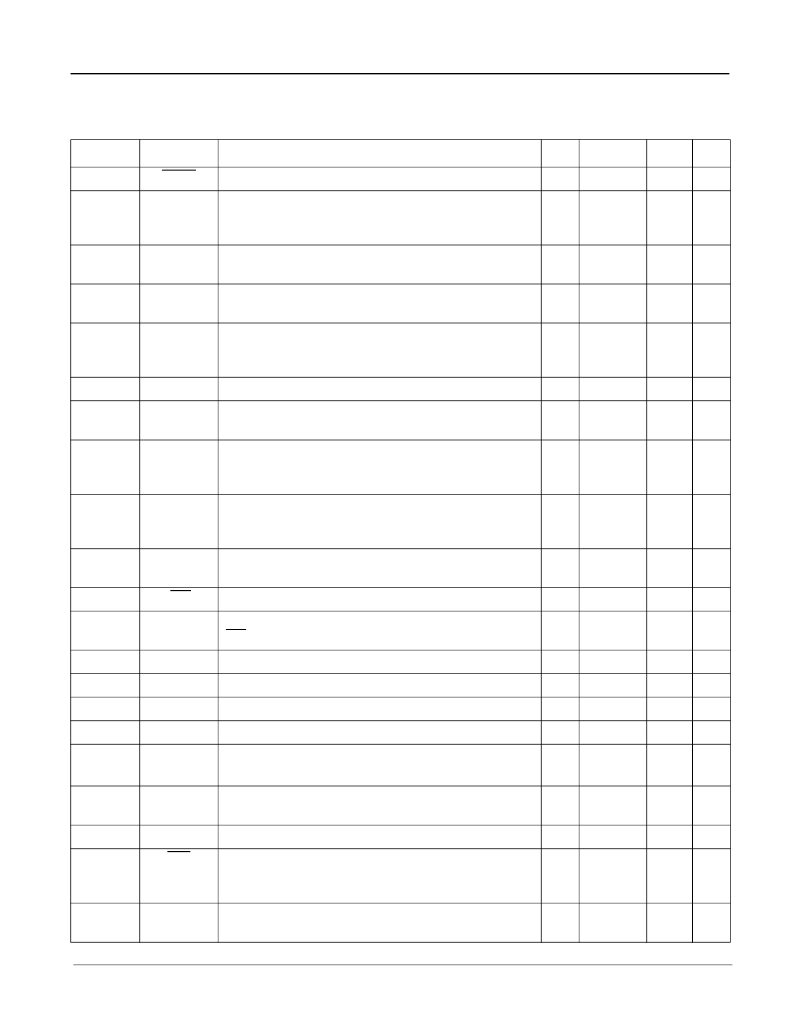

4.6 ZL10313 Pinout Description

Pin Description Table

Pin

Name

Description

I/O

Note

V

mA

1

Reset

Active low reset input

I

CMOS

1

5

2

DiSEqC[2]

DiSEqC input for level 2 control. Also usable as

GPP2 (general purpose port pin) for other purposes,

and as MICLK - external clock input for MPEG data.

I/O

Open

drain

1

5

6

3

DiSEqC[1]

Horizontal/vertical LNB control (acts as input only in

production test modes)

I/O

CMOS

3.3

2

4

DiSEqC[0]

22 kHz output to LNB (acts as input only in

production test modes)

I/O

CMOS

3.3

2

9

Sleep

Stops oscillator and sets minimum power levels to

entire device (except ADCs - register controlled

power-down)

I

CMOS

3.3

10

CLK1

Primary 2-wire serial bus clock

I

CMOS

1

5

11

DATA1

Primary 2-wire serial bus data

I/O

Open

drain

1

5

6

14

DATA2

Secondary 2-wire bus data to tuner front end. Also

usable as GPP1 (general purpose port pin) for other

purposes.

I/O

Open

drain

1

5

6

15

CLK2

Secondary 2-wire bus clock to tuner front end. Also

usable as GPP0 (general purpose port pin) for other

purposes.

I/O

Open

drain

1

5

6

16

OscMode

Controls oscillator mode to suit crystal or external

signal

I

CMOS

3.3

19

XTI

Crystal input or external reference clock input

I

CMOS

1.8

20

XTO

Crystal output, includes internal feedback resistor to

XTI

I/O

CMOS

1.8

24

Iin

I channel input

I

analog

25

Iin

I channel negative input

I

analog

29

Qin

Q channel negative input

I

analog

30

Qin

Q channel input

I

analog

35,36,37

38

ADDR[1:4]

Primary 2-wire bus address defining pins

I

CMOS

3.3

41

AGC

AGC sigma-delta output (acts as input only in

production test modes)

I/O

Open

drain

1

5

6

42

Test

For normal operation, this pin must be held at 0 V.

I

CMOS

3.3

43

IRQ

Active low interrupt output. Reading all active

interrupt registers resets this pin. Can also be defined

as MICLK - external clock input for MPEG data

I/O

Open

drain

1

5

6

46

MOSTRT

MPEG output start signal. High during the first byte of

a packet.

O

CMOS

Tri-state

3.3

2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL10313UBH | WIRE, PTFE, A, WHITE, 7/.012MM, 100M; Area, conductor CSA:0.079mm2; Conductor make-up:7/0.12mm; Voltage rating, AC:300V; Current rating:3A; Colour, primary insulation:White; Material, primary insulation:PTFE; Diameter, RoHS Compliant: Yes |

| ZL10313 | Satellite Demodulator |

| ZL10353QCF | Fully Compliant NorDig Unified COFDM Digital Terrestrial TV (DTV) Demodulator |

| ZL10353QCF1 | Fully Compliant NorDig Unified COFDM Digital Terrestrial TV (DTV) Demodulator |

| ZL10353QCG | Fully Compliant NorDig Unified COFDM Digital Terrestrial TV (DTV) Demodulator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL10313UBH | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Satellite Demodulator |

| ZL10320 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Digital Television PVR-on-a-Chip Processor |

| ZL10320/GAC | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Digital Television PVR-on-a-Chip Processor |

| ZL10321/GAC | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Digital Television PVR-on-a-Chip Processor |

| ZL10353 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Fully Compliant NorDig Unified COFDM Digital Terrestrial TV (DTV) Demodulator |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。