- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373782 > ZL10036LDG1 (ZARLINK SEMICONDUCTOR INC) Digital Satellite Tuner with RF Bypass PDF資料下載

參數(shù)資料

| 型號(hào): | ZL10036LDG1 |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | Digital Satellite Tuner with RF Bypass |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, QCC40 |

| 封裝: | 6 X 6 MM, LEAD FREE, QFN-40 |

| 文件頁(yè)數(shù): | 20/38頁(yè) |

| 文件大?。?/td> | 939K |

| 代理商: | ZL10036LDG1 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)

ZL10036

Data Sheet

20

Zarlink Semiconductor Inc.

3.2 Device Address Selection

Two internal logic levels,

MA1

and

MA0

, can be set to one of four possible logic states by the voltage applied to the

ADD

pin (#16). These four states in turn define four different read and write addresses on the I2C bus, so that as

many as four separate devices can be individually addressed on one bus. This is of particular use in a multi-tuner

environment as required by PVR applications.

3.3 Read Register

The ZL10036 status can be read by addressing the device in its slave transmitter mode by setting the LSB of the

address byte (the R/W bit) to a one. After the master transmits the correct address byte, the ZL10036 will

acknowledge its address, and transmit data in response to further clocks on the SCL input. If the master responds

with an acknowledge and further clocks, the status byte will be retransmitted until such time as the master fails to

send an acknowledge, when the ZL10036 will release the data bus, allowing the master to generate a stop

condition.

The individual bits in the status register have the following meanings:

3.3.1 Power-On Reset Indicator (POR bit)

This bit is set to a logic ‘1’ if the VccDIG supply to the PLL section has dropped below typically 3.6 V, e.g., when the

device is initially turned on. The bit is reset to ‘0’ when the read sequence is terminated by a STOP command.

When the POR bit is high, this indicates that the programmed information may have been corrupted and the device

reset to power up condition.

3.3.2 Frequency & Phase Lock (FL bit)

Bit 6 (FL) indicates whether the synthesizer is phase locked, a logic ‘1’ is present if the device is locked, and a logic

‘0’ if the device is unlocked.

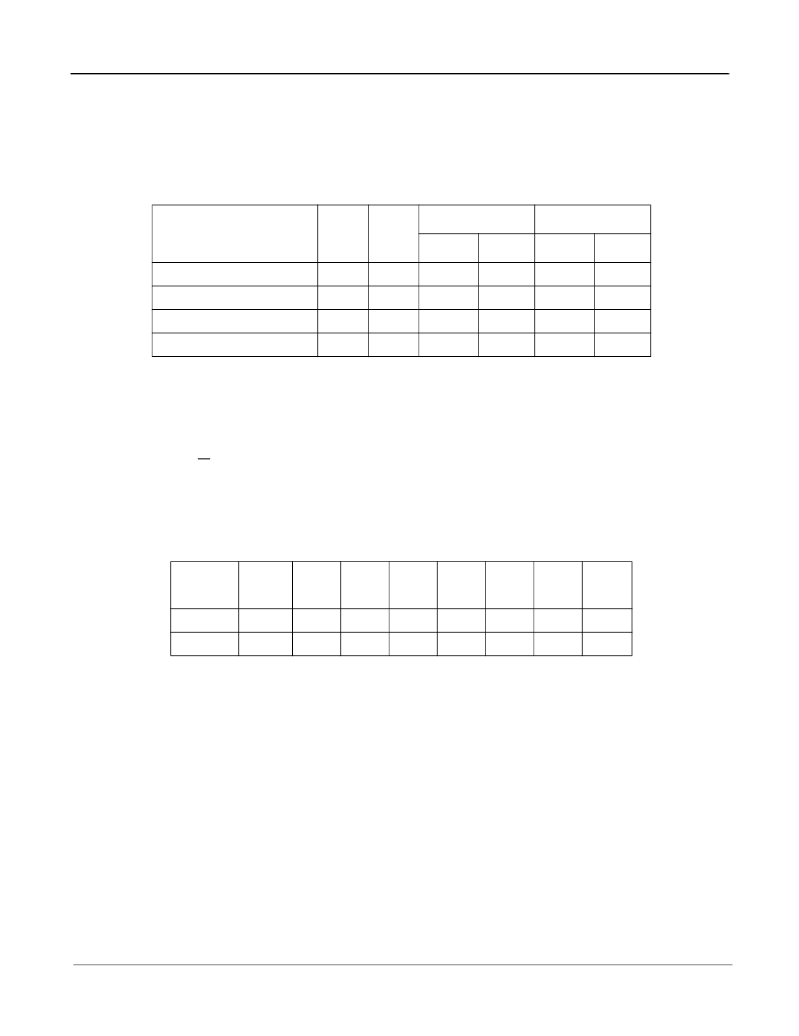

ADD Pin Voltage

MA1

MA0

Write Address

Read Address

Hex.

Dec.

Hex.

Dec.

Vee (0 V or Gnd)

0

0

0xC0

192

0xC1

193

Open circuit

0.5 * DIGDEC (±20%)

1

0

1

0xC2

194

0xC3

195

1. can be programmed with a single 30 k

resistor to DIGDEC

1

0

0xC4

196

0xC5

197

DIGDEC

1

1

0xC6

198

0xC7

199

Table 3 - Address Selection

Bit No.

7

(MSB)

6

5

4

3

2

1

0

(LSB)

Address

1

1

0

0

0

MA1

MA0

1

Status

POR

FL

X

X

X

X

X

X

Table 4 - Read Data Bit Format (MSB is Transmitted First)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL10039LCF1 | MULTIMETER, DIGITAL; Accuracy, AC current range:+/-(1.5% + 3d); Accuracy, AC voltage range:+/-(1.3% + 5d); Accuracy, DC current range:+/-(1.5% + 3d); Accuracy, DC voltage range:+/-(0.8% + 3d); Accuracy, resistance range:+/-(1.5% + RoHS Compliant: NA |

| ZL10039LCG | 100A clamp for PQ meters RoHS Compliant: NA |

| ZL10039LCG1 | Test, Recorder RoHS Compliant: NA |

| ZL10039 | Digital Satellite Tuner with RF Bypass |

| ZL10039LCF | Digital Satellite Tuner with RF Bypass |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL10037 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Digital Satellite Tuner with RF Bypass |

| ZL10037LCF | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Digital Satellite Tuner with RF Bypass |

| ZL10037LCF1 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Digital Satellite Tuner with RF Bypass |

| ZL10037LCG | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Digital Satellite Tuner with RF Bypass |

| ZL10037LCG1 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Digital Satellite Tuner with RF Bypass |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。