- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376460 > XRK69774CR (EXAR CORP) 1:14 LVCMOS PLL CLOCK GENERATOR PDF資料下載

參數(shù)資料

| 型號: | XRK69774CR |

| 廠商: | EXAR CORP |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 1:14 LVCMOS PLL CLOCK GENERATOR |

| 中文描述: | 69774 SERIES, PLL BASED CLOCK DRIVER, 12 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| 封裝: | 10 X 10 MM, 1.40 MM HEIGHT, LQFP-52 |

| 文件頁數(shù): | 1/11頁 |

| 文件大小: | 84K |

| 代理商: | XRK69774CR |

Exar

Corporation 48720 Kato Road, Fremont CA, 94538

(510) 668-7000

FAX (510) 668-7017

www.exar.com

PRELIMINARY

XRK69774

1:14 LVCMOS PLL CLOCK GENERATOR

APRIL 2006

REV. P1.0.1

GENERAL DESCRIPTION

The XRK69774 is a PLL based LVCMOS Clock Generator

targeted for high performance and low skew clock distribu-

tion applications. The XRK69774 can select between one

of two reference inputs and provides 15 LVCMOS outputs -

14 outputs (2 banks of 5 and 1 bank of 4) for clock distribu-

tion and 1 for feedback.

The XRK69774 has two LVCMOS inputs to support clock

redundancy. Switching the internal reference clock is con-

trolled by the control input, CLK_SEL.

The XRK69774 uses PLL technology to frequency lock its

outputs to the input reference clock. The divider in the feed-

back path will determine the frequency of the VCO. Each of

the separate output banks can individually divide down the

VCO output frequency. This allows the XRK69774 to gen-

erate a multitude of different bank frequency ratios and out-

put-to-input frequency ratios.

The outputs of the XRK69774 can be immobilized, in the

low state, by use of the stop clock feature. Global output

disabling and reset can be achieved with the control input

MR/OE.

The XRK69774 has an output frequency range of 8.33MHz

to125MHz and an input frequency range of 4.16MHz to

62.5MHz.

FEATURES

Fully Integrated PLL

15 LVCMOS outputs

■

2 banks with 5 outputs and 1 with 4 outputs

each

■

1 dedicated feedback for frequency control

■

Output Frequency of each Bank can be

individually controlled

VCO Range 200MHz to 500MHz

Output freq. range: 8.33MHz to 125MHz

Max Output Skew of 175ps

Max Cycle-to-cycle jitter: 90ps

LVCMOS inputs for reference clock source

APPLICATIONS

System Clock generator

Zero Delay Buffer

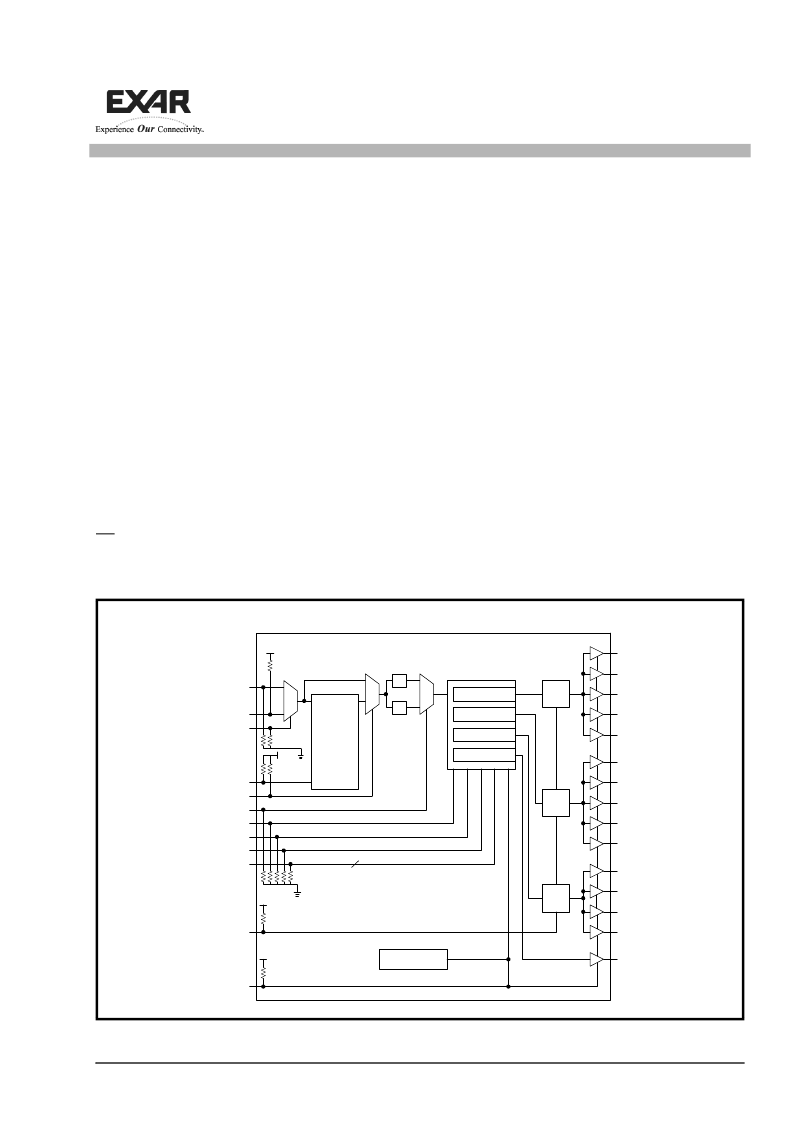

F

IGURE

1. B

LOCK

D

IAGRAM

OF

THE

XRK69774

STOP

CLK

STOP

CLK

0

1

÷4

0

1

0

1

POR

÷2, ÷4

÷2, ÷4

÷4, ÷6

÷4, ÷6, ÷8, ÷12

÷2

2

PLL

200-500MHz

FB

Ref

VCO

STOP

CLK

VDD

VDD

VDD

VDD

CLK0

CLK1

CLK_SEL

FB_IN

PLL_EN

VCO_SEL

FSEL_A

FSEL_B

FSEL_C

FSEL_FB[1:0]

__________

STOP_CLK

___

MR/OE

QA0

QA1

QA2

QA3

QA4

QB0

QB1

QB2

QB3

QB4

QC0

QC1

QC2

QC3

QFB

Divider Select

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRK69774IR | 1:14 LVCMOS PLL CLOCK GENERATOR |

| XRK697H73 | 1:12 LVCMOS PLL CLOCK GENERATOR |

| XRK697H73CR | 1:12 LVCMOS PLL CLOCK GENERATOR |

| XRK697H73IR | 1:12 LVCMOS PLL CLOCK GENERATOR |

| XRK7933 | INTELLIGENT DYNAMIC CLOCK SWITCH PLL CLOCK DRIVER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRK69774IR | 制造商:EXAR 制造商全稱:EXAR 功能描述:1:14 LVCMOS PLL CLOCK GENERATOR |

| XRK697H73 | 制造商:EXAR 制造商全稱:EXAR 功能描述:1:12 LVCMOS PLL CLOCK GENERATOR |

| XRK697H73CR | 制造商:EXAR 制造商全稱:EXAR 功能描述:1:12 LVCMOS PLL CLOCK GENERATOR |

| XRK697H73IR | 制造商:EXAR 制造商全稱:EXAR 功能描述:1:12 LVCMOS PLL CLOCK GENERATOR |

| XRK7933 | 制造商:EXAR 制造商全稱:EXAR 功能描述:INTELLIGENT DYNAMIC CLOCK SWITCH PLL CLOCK DRIVER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。