- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376460 > XRK69772IR (EXAR CORP) 1:12 LVCMOS PLL CLOCK GENERATOR PDF資料下載

參數(shù)資料

| 型號: | XRK69772IR |

| 廠商: | EXAR CORP |

| 元件分類: | XO, clock |

| 英文描述: | 1:12 LVCMOS PLL CLOCK GENERATOR |

| 中文描述: | 240 MHz, OTHER CLOCK GENERATOR, PQFP52 |

| 封裝: | 10 X 10 MM, 1.40 MM HEIGHT, LQFP-52 |

| 文件頁數(shù): | 7/12頁 |

| 文件大?。?/td> | 97K |

| 代理商: | XRK69772IR |

PRELIMINARY

XRK69772

7

REV. P1.0.0

1:12 LVCMOS PLL CLOCK GENERATOR

2.0

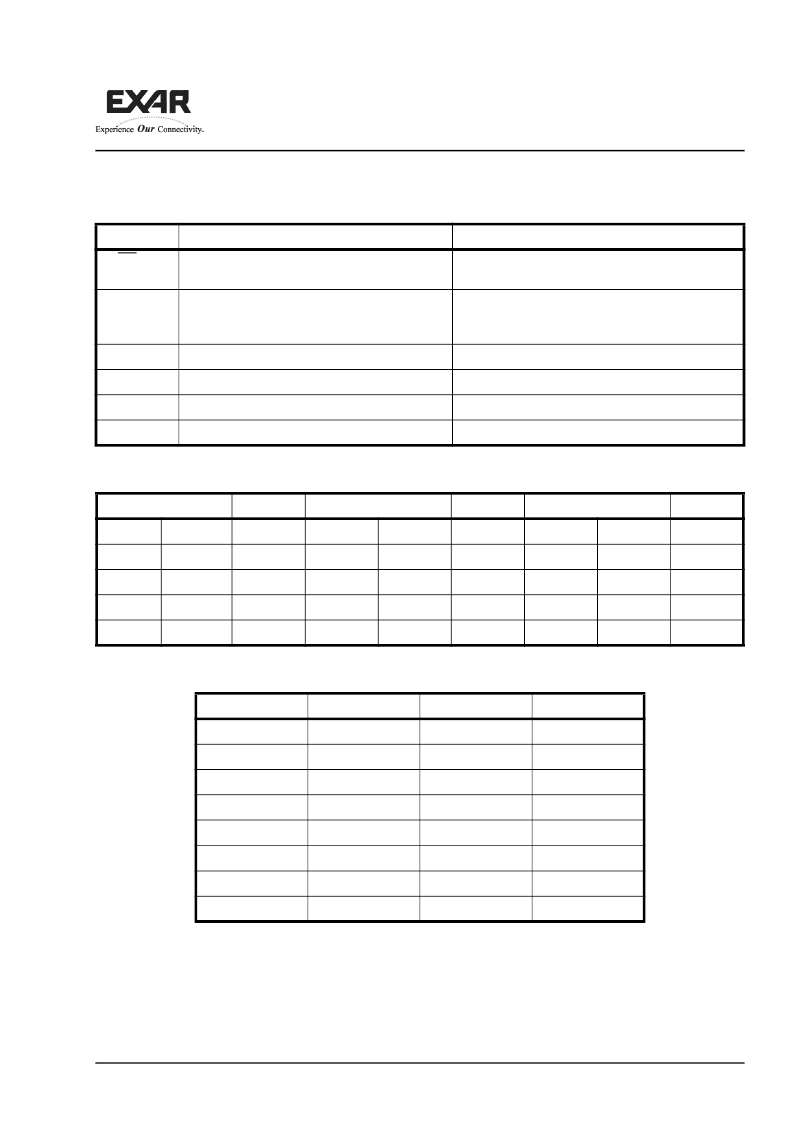

CONFIGURATION TABLES

T

ABLE

6: F

UNCTION

C

ONTROLS

C

ONTROL

P

IN

L

OGIC

0

L

OGIC

1

MR/OE

Resets the output divide circuitry and serial inter-

face, tri-states all outputs

Enables all outputs - normal operation

PLL_SEL

PLL bypass mode enabled. This is a test mode in

which the reference clock is provided to the output

dividers in place of the VCO.

PLL enabled - normal operation

REF_SEL

CLKx selected as ref source to PLL

Crystal Oscillator selected as ref source to PLL.

CLK_SEL

CLK0 selected

CLK1 selected

INV_CLK

QC2 & QC3 are in phase with QC1 & QC4

QC2 & QC3 are 180° out of phase with QC1 & QC4

VCO_SEL

VCO ÷ 2

no divide of VCO

T

ABLE

7: B

ANK

O

UTPUT

D

IVIDER

C

ONTROLS

INPUT

OUTPUT

INPUT

OUTPUT

INPUT

OUTPUT

FSEL_A1

FSEL_A0

QA

FSEL_B1

FSEL_B0

QB

FSEL_C1

FSEL_C0

QC

0

0

÷4

0

0

÷4

0

0

÷2

0

1

÷6

0

1

÷6

0

1

÷4

1

0

÷8

1

0

÷8

1

0

÷6

1

1

÷12

1

1

÷10

1

1

÷8

T

ABLE

8: F

EEDBACK

D

IVIDER

C

ONTROL

FSEL_FB2

FSEL_FB1

FSEL_FB0

QFB

0

0

0

÷4

0

0

1

÷6

0

1

0

÷8

0

1

1

÷10

1

0

0

÷8

1

0

1

÷12

1

1

0

÷16

1

1

1

÷20

相關PDF資料 |

PDF描述 |

|---|---|

| XRK69773 | 1:12 LVCMOS PLL CLOCK GENERATOR |

| XRK69773CR | 1:12 LVCMOS PLL CLOCK GENERATOR |

| XRK69773IR | 1:12 LVCMOS PLL CLOCK GENERATOR |

| XRK69774 | 1:14 LVCMOS PLL CLOCK GENERATOR |

| XRK69774CR | 1:14 LVCMOS PLL CLOCK GENERATOR |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XRK69773 | 制造商:EXAR 制造商全稱:EXAR 功能描述:1:12 LVCMOS PLL CLOCK GENERATOR |

| XRK69773CR | 制造商:EXAR 制造商全稱:EXAR 功能描述:1:12 LVCMOS PLL CLOCK GENERATOR |

| XRK69773IR | 制造商:EXAR 制造商全稱:EXAR 功能描述:1:12 LVCMOS PLL CLOCK GENERATOR |

| XRK69774 | 制造商:EXAR 制造商全稱:EXAR 功能描述:1:14 LVCMOS PLL CLOCK GENERATOR |

| XRK69774CR | 制造商:EXAR 制造商全稱:EXAR 功能描述:1:14 LVCMOS PLL CLOCK GENERATOR |

發(fā)布緊急采購,3分鐘左右您將得到回復。