- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16523 > XR16V2652IL-0B-EB (Exar Corporation)EVAL BOARD FOR V2652 32QFN PDF資料下載

參數(shù)資料

| 型號: | XR16V2652IL-0B-EB |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 36/48頁 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR V2652 32QFN |

| 標(biāo)準包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁當(dāng)前第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

XR16V2652

41

REV. 1.0.2

HIGH PERFORMANCE DUART WITH 32-BYTE FIFO

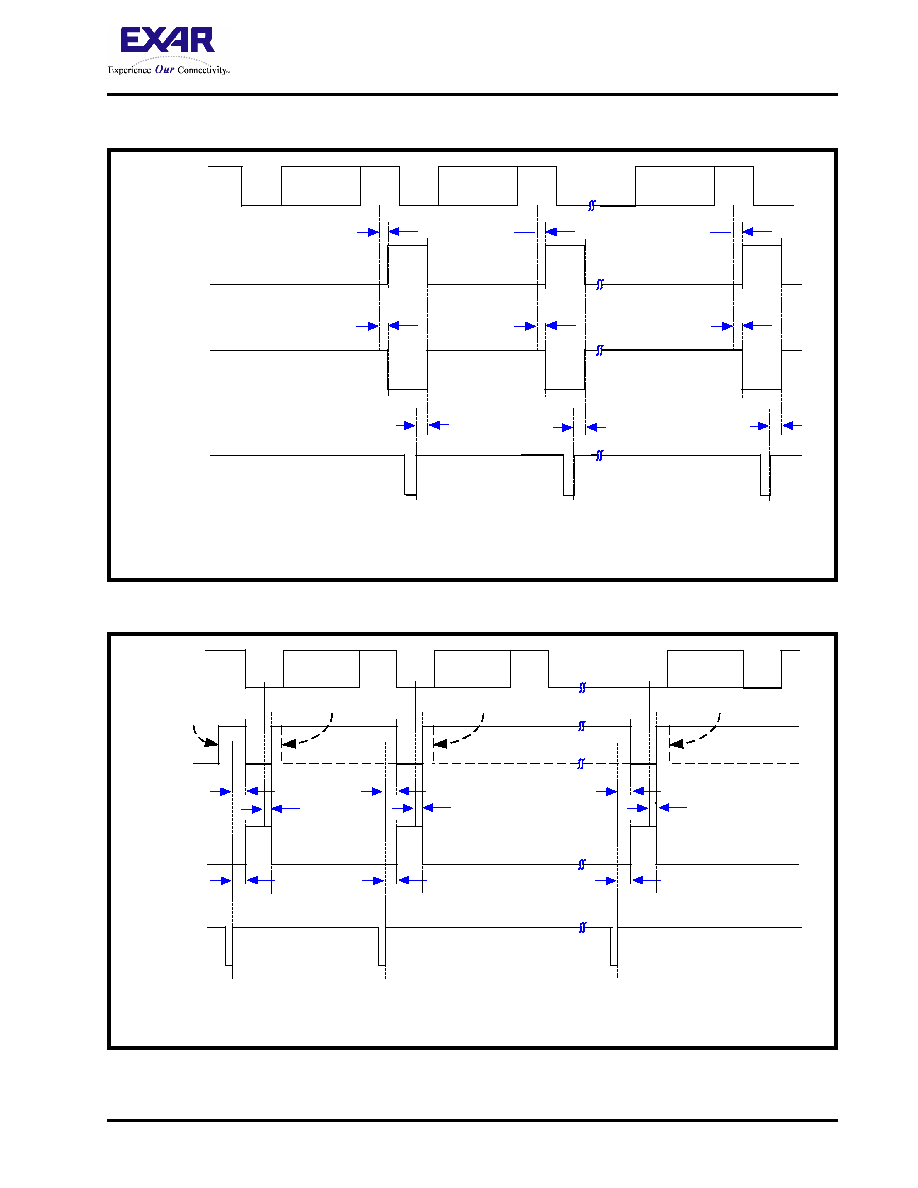

FIGURE 17. RECEIVE READY & INTERRUPT TIMING [NON-FIFO MODE] FOR CHANNELS A & B

FIGURE 18. TRANSMIT READY & INTERRUPT TIMING [NON-FIFO MODE] FOR CHANNELS A & B

RX

RXRDY#

IOR#

INT

D0:D7

Start

Bit

D0:D7

Stop

Bit

D0:D7

T

SSR

1 Byte

in RHR

Active

Data

Ready

Active

Data

Ready

Active

Data

Ready

1 Byte

in RHR

1 Byte

in RHR

T

SSR

T

SSR

RXNFM

T

RR

T

RR

T

RR

T

SSR

T

SSR

T

SSR

(Reading data

out of RHR)

TX

TXRDY#

IOW#

INT*

D0:D7

Start

Bit

D0:D7

Stop

Bit

D0:D7

T

WT

TXNonFIFO

T

WT

T

WT

T

WRI

T

WRI

T

WRI

T

SRT

T

SRT

T

SRT

*INT is cleared when the ISR is read or when data is loaded into the THR.

ISR is read

(Loading data

into THR)

IER[1]

enabled

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5022-392J | INDUCTOR 3.90UH 5% TOLERANCE SMD |

| GSM11DRTN-S13 | CONN EDGECARD 22POS .156 EXTEND |

| RCM10DTKI-S288 | CONN EDGECARD 20POS .156 EXTEND |

| A3DDB-1636G | IDC CABLE- AKR16B/AE16G/AKR16B |

| MCP1316T-29LE/OT | IC SUPERVISOR 2.90V P-P SOT23-5 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR16V2652IL32 | 制造商:EXAR 制造商全稱:EXAR 功能描述:HIGH PERFORMANCE DUART WITH 32-BYTE FIFO |

| XR16V2652IL-F | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16V2652ILTR-F | 制造商:Exar Corporation 功能描述:UART 2-CH 32Byte FIFO 2.5V/3.3V 32-Pin QFN EP T/R 制造商:Exar Corporation 功能描述:XR16V2652ILTR-F |

| XR16V2750 | 制造商:EXAR 制造商全稱:EXAR 功能描述:HIGH PERFORMANCE DUART WITH 64-BYTE FIFO |

| XR16V2750_07 | 制造商:EXAR 制造商全稱:EXAR 功能描述:HIGH PERFORMANCE DUART WITH 64-BYTE FIFO |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。