- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4205 > XCV1000E-6FG1156I (Xilinx Inc)IC FPGA 1.8V I-TEMP 1156-FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | XCV1000E-6FG1156I |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 35/233頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA 1.8V I-TEMP 1156-FBGA |

| 產(chǎn)品變化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | Virtex®-E |

| LAB/CLB數(shù): | 6144 |

| 邏輯元件/單元數(shù): | 27648 |

| RAM 位總計(jì): | 393216 |

| 輸入/輸出數(shù): | 660 |

| 門數(shù): | 1569178 |

| 電源電壓: | 1.71 V ~ 1.89 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 1156-BBGA |

| 供應(yīng)商設(shè)備封裝: | 1156-FBGA(35x35) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)當(dāng)前第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)第206頁(yè)第207頁(yè)第208頁(yè)第209頁(yè)第210頁(yè)第211頁(yè)第212頁(yè)第213頁(yè)第214頁(yè)第215頁(yè)第216頁(yè)第217頁(yè)第218頁(yè)第219頁(yè)第220頁(yè)第221頁(yè)第222頁(yè)第223頁(yè)第224頁(yè)第225頁(yè)第226頁(yè)第227頁(yè)第228頁(yè)第229頁(yè)第230頁(yè)第231頁(yè)第232頁(yè)第233頁(yè)

Virtex-E 1.8 V Field Programmable Gate Arrays

R

DS022-2 (v3.0) March 21, 2014

Module 2 of 4

Production Product Specification

7

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

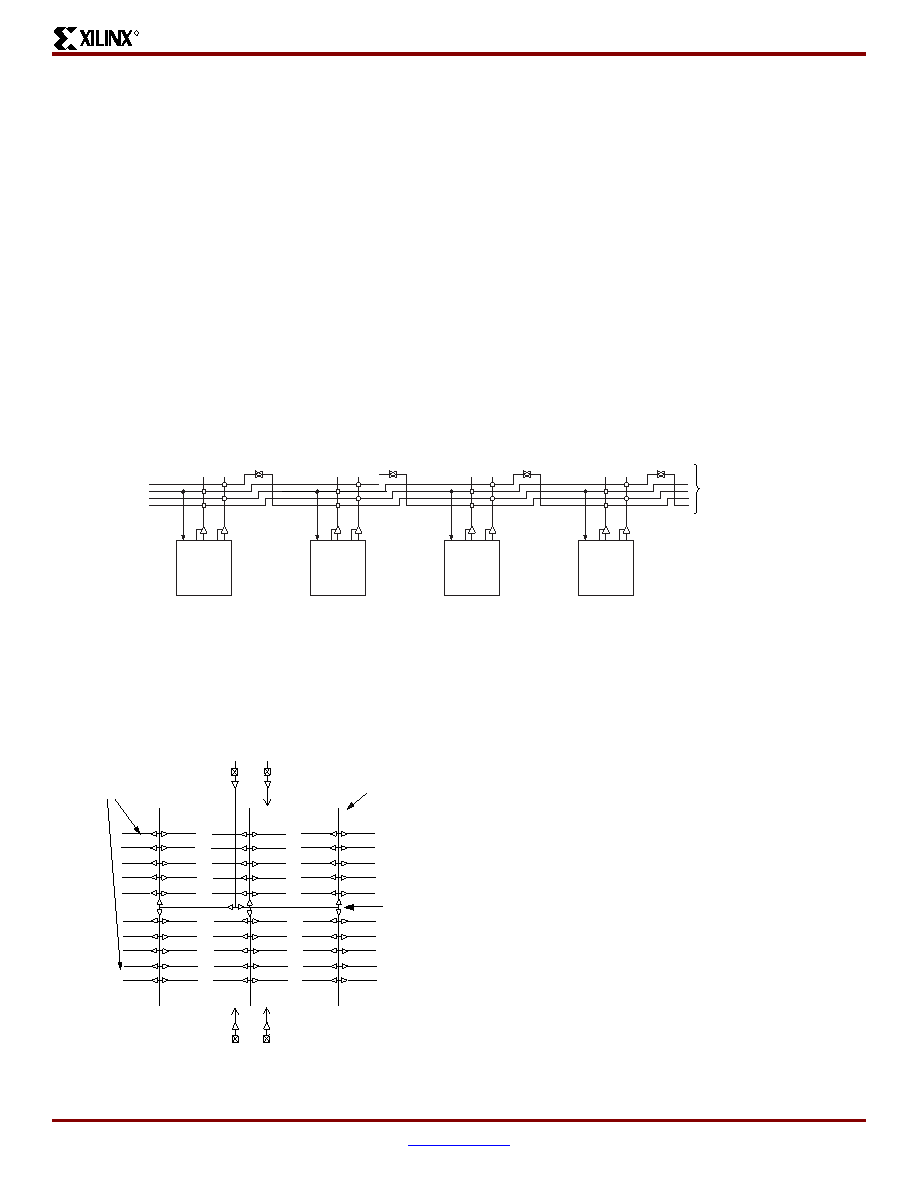

Dedicated Routing

Some classes of signal require dedicated routing resources to

maximize performance. In the Virtex-E architecture, dedi-

cated routing resources are provided for two classes of signal.

Horizontal routing resources are provided for on-chip

3-state buses. Four partitionable bus lines are provided

per CLB row, permitting multiple buses within a row, as

shown in Figure 8.

Two dedicated nets per CLB propagate carry signals

vertically to the adjacent CLB.Global Clock Distribution

Network

DLL Location

Clock Routing

Clock Routing resources distribute clocks and other signals

with very high fanout throughout the device. Virtex-E

devices include two tiers of clock routing resources referred

to as global and local clock routing resources.

The global routing resources are four dedicated global

nets with dedicated input pins that are designed to

distribute high-fanout clock signals with minimal skew.

Each global clock net can drive all CLB, IOB, and block

RAM clock pins. The global nets can be driven only by

global buffers. There are four global buffers, one for

each global net.

The local clock routing resources consist of 24

backbone lines, 12 across the top of the chip and 12

across bottom. From these lines, up to 12 unique

signals per column can be distributed via the 12

longlines in the column. These local resources are

more flexible than the global resources since they are

not restricted to routing only to clock pins.

Global Clock Distribution

Virtex-E provides high-speed, low-skew clock distribution

through the global routing resources described above. A

typical clock distribution net is shown in Figure 9.

Four global buffers are provided, two at the top center of the

device and two at the bottom center. These drive the four

global nets that in turn drive any clock pin.

Four dedicated clock pads are provided, one adjacent to

each of the global buffers. The input to the global buffer is

selected either from these pads or from signals in the gen-

eral purpose routing.

Digital Delay-Locked Loops

There are eight DLLs (Delay-Locked Loops) per device,

with four located at the top and four at the bottom,

Figure 10. The DLLs can be used to eliminate skew

between the clock input pad and the internal clock input pins

throughout the device. Each DLL can drive two global clock

networks.The DLL monitors the input clock and the distrib-

uted clock, and automatically adjusts a clock delay element.

Additional delay is introduced such that clock edges arrive

at internal flip-flops synchronized with clock edges arriving

at the input.

In addition to eliminating clock-distribution delay, the DLL

provides advanced control of multiple clock domains. The

DLL provides four quadrature phases of the source clock,

and can double the clock or divide the clock by 1.5, 2, 2.5, 3,

4, 5, 8, or 16.

Figure 8: BUFT Connections to Dedicated Horizontal Bus LInes

CLB

buft_c.eps

Tri-State

Lines

Figure 9: Global Clock Distribution Network

Gl

ob

al

Clo

c

k

Sp

in

e

Global Clock Column

GCLKPAD2

GCLKBUF2

GCLKPAD3

GCLKBUF3

GCLKBUF1

GCLKPAD1

GCLKBUF0

GCLKPAD0

Global Clock Rows

XCVE_009

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GCB106DHBR-S621 | CONN EDGECARD 212PS R/A .050 SLD |

| AMM36DSEI | CONN EDGECARD 72POS .156 EYELET |

| AMM36DRTI | CONN EDGECARD 72POS DIP .156 SLD |

| HMC49DRYS-S734 | CONN EDGECARD 98POS DIP .100 SLD |

| XC5VFX100T-1FFG1738C | IC FPGA VIRTEX 5 100K 1738FFGBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCV1000E-6FG240C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex⑩-E 1.8 V Field Programmable Gate Arrays |

| XCV1000E-6FG240I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Field Programmable Gate Arrays |

| XCV1000E6FG680C | 制造商:XILINX 功能描述:New |

| XCV1000E-6FG680C | 功能描述:IC FPGA 1.8V C-TEMP 680-FGBA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:Virtex®-E 產(chǎn)品變化通告:Step Intro and Pkg Change 11/March/2008 標(biāo)準(zhǔn)包裝:1 系列:Virtex®-5 SXT LAB/CLB數(shù):4080 邏輯元件/單元數(shù):52224 RAM 位總計(jì):4866048 輸入/輸出數(shù):480 門數(shù):- 電源電壓:0.95 V ~ 1.05 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:1136-BBGA,F(xiàn)CBGA 供應(yīng)商設(shè)備封裝:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XCV1000E-6FG680I | 功能描述:IC FPGA 1.8V I-TEMP 680-FGBA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:Virtex®-E 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標(biāo)準(zhǔn)包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計(jì):3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應(yīng)商設(shè)備封裝:120-CPGA(34.55x34.55) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。