- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4141 > XCS30XL-4VQ100I (Xilinx Inc)IC FPGA 3.3V I-TEMP HP 100VQFP PDF資料下載

參數(shù)資料

| 型號: | XCS30XL-4VQ100I |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 67/83頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA 3.3V I-TEMP HP 100VQFP |

| 產(chǎn)品變化通告: | Product Discontinuation 26/Oct/2011 |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | Spartan®-XL |

| LAB/CLB數(shù): | 576 |

| 邏輯元件/單元數(shù): | 1368 |

| RAM 位總計: | 18432 |

| 輸入/輸出數(shù): | 77 |

| 門數(shù): | 30000 |

| 電源電壓: | 3 V ~ 3.6 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 100-TQFP |

| 供應(yīng)商設(shè)備封裝: | 100-VQFP(14x14) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁當(dāng)前第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁

Spartan and Spartan-XL FPGA Families Data Sheet

DS060 (v2.0) March 1, 2013

Product Specification

R

Product Obsolete/Under Obsolescence

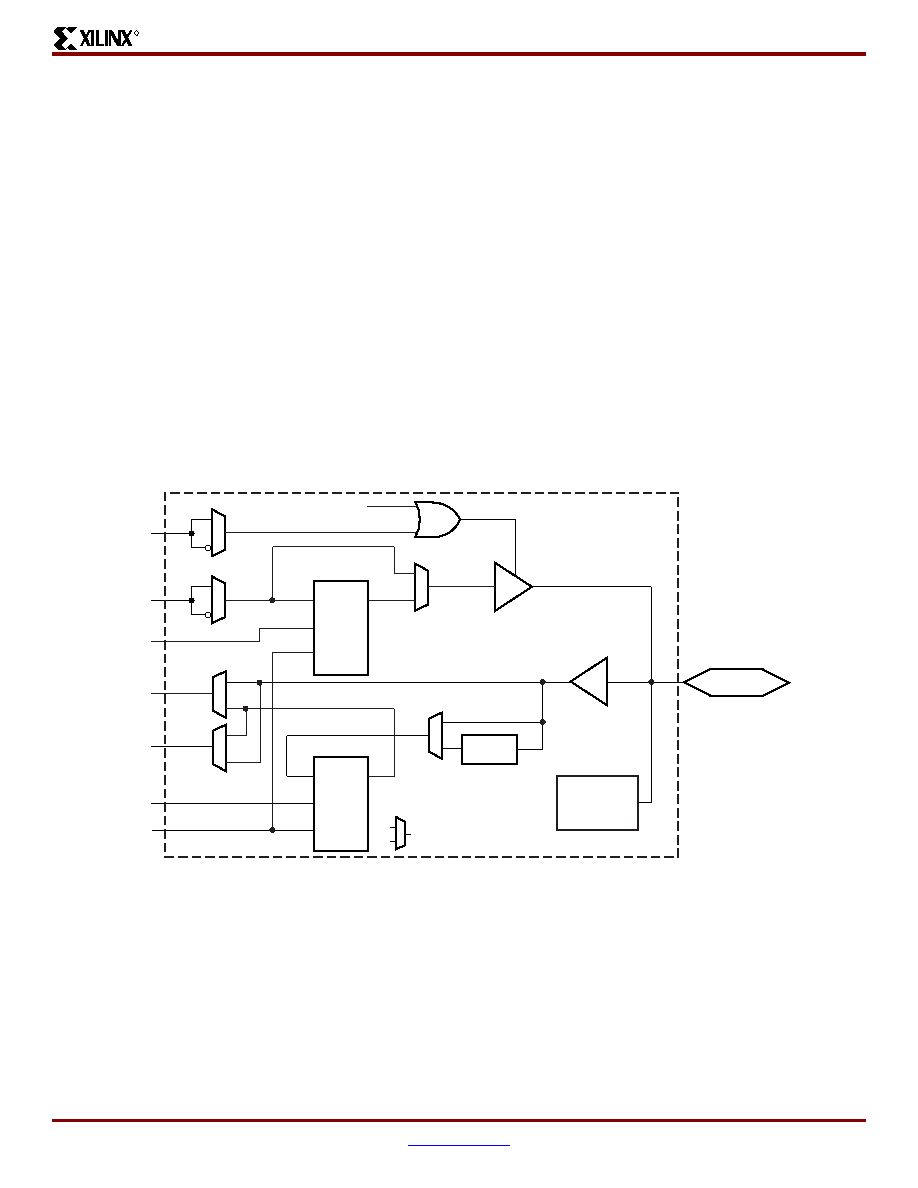

The register choice is made by placing the appropriate

library symbol. For example, IFD is the basic input flip-flop

(rising edge triggered), and ILD is the basic input latch

(transparent-High). Variations with inverted clocks are also

available. The clock signal inverter is also shown in Figure 5

on the CK line.

The Spartan family IOB data input path has a one-tap delay

element: either the delay is inserted (default), or it is not.

The Spartan-XL family IOB data input path has a two-tap

delay element, with choices of a full delay, a partial delay, or

no delay. The added delay guarantees a zero hold time with

respect to clocks routed through the global clock buffers.

(See Global Nets and Buffers, page 12 for a description of

the global clock buffers in the Spartan/XL families.) For a

shorter input register setup time, with positive hold-time,

attach a NODELAY attribute or property to the flip-flop.The

output of the input register goes to the routing channels (via

I1 and I2 in Figure 6). The I1 and I2 signals that exit the IOB

can each carry either the direct or registered input signal.

The 5V Spartan family input buffers can be globally config-

ured for either TTL (1.2V) or CMOS (VCC/2) thresholds,

using an option in the bitstream generation software. The

Spartan family output levels are also configurable; the two

global adjustments of input threshold and output level are

independent. The inputs of Spartan devices can be driven

by the outputs of any 3.3V device, if the Spartan family

inputs are in TTL mode. Input and output thresholds are

TTL on all configuration pins until the configuration has

been loaded into the device and specifies how they are to

be used. Spartan-XL family inputs are TTL compatible and

3.3V CMOS compatible.

Supported sources for Spartan/XL device inputs are shown

in Table 4.

Spartan-XL family I/Os are fully 5V tolerant even though the

VCC is 3.3V. This allows 5V signals to directly connect to the

Spartan-XL family inputs without damage, as shown in

after 5V signals are applied to the I/Os. This makes the

Spartan-XL devices immune to power supply sequencing

problems.

Figure 6: Simplified Spartan/XL IOB Block Diagram

Multiplexer Controlled

by Configuration Program

T

O

OK

Q

GTS

D

CK

EC

I1

I2

IK

EC

Q

D

CK

EC

Delay

Package

Pad

Programmable

Pull-Up/

Pull-Down

Network

OUTPUT DRIVER

Programmable Slew Rate

Programmable TTL/CMOS Drive

(Spartan only)

INPUT BUFFER

DS060_06_041901

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT71V3558SA166BQG | IC SRAM 4MBIT 166MHZ 165FBGA |

| IDT71V424L10YGI | IC SRAM 4MBIT 10NS 36SOJ |

| IDT7130SA100JI | IC SRAM 8KBIT 100NS 52PLCC |

| IDT7140LA55P | IC SRAM 8KBIT 55NS 48DIP |

| IDT7140LA100P | IC SRAM 8KBIT 100NS 48DIP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCS30XL-4VQ144C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS30XL-4VQ144I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS30XL-4VQ208C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS30XL-4VQ208I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS30XL-4VQ240C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。