- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄3987 > XCS20XL-5TQ144C (Xilinx Inc)IC FPGA 3.3V C-TEMP HP 144TQFP PDF資料下載

參數(shù)資料

| 型號: | XCS20XL-5TQ144C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 61/83頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 3.3V C-TEMP HP 144TQFP |

| 產(chǎn)品變化通告: | Product Discontinuation 26/Oct/2011 |

| 標準包裝: | 60 |

| 系列: | Spartan®-XL |

| LAB/CLB數(shù): | 400 |

| 邏輯元件/單元數(shù): | 950 |

| RAM 位總計: | 12800 |

| 輸入/輸出數(shù): | 113 |

| 門數(shù): | 20000 |

| 電源電壓: | 3 V ~ 3.6 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 144-LQFP |

| 供應(yīng)商設(shè)備封裝: | 144-TQFP(20x20) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁當前第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁

Spartan and Spartan-XL FPGA Families Data Sheet

64

DS060 (v2.0) March 1, 2013

Product Specification

R

Product Obsolete/Under Obsolescence

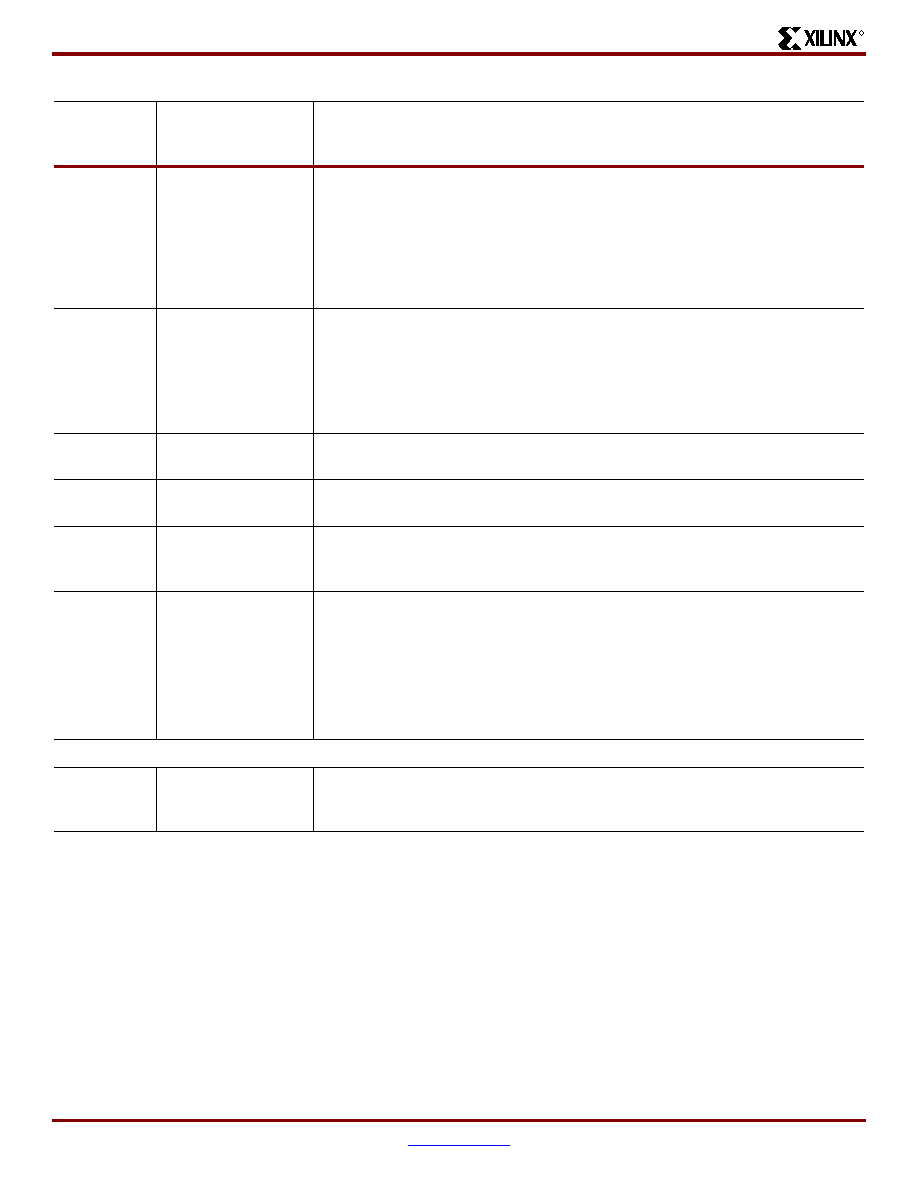

SGCK1 -

SGCK4

(Spartan)

Weak

Pull-up

(except

SGCK4

is DOUT)

I or I/O

Four Secondary Global inputs each drive a dedicated internal global net with short

delay and minimal skew. These internal global nets can also be driven from

internal logic. If not used to drive a global net, any of these pins is a

user-programmable I/O pin.

The SGCK1-SGCK4 pins provide the shortest path to the four Secondary Global

Buffers. Any input pad symbol connected directly to the input of a BUFGS symbol

is automatically placed on one of these pins.

GCK1 -

GCK8

(Spartan-XL)

Weak

Pull-up

(except

GCK6 is

DOUT)

I or I/O

Eight Global inputs each drive a dedicated internal global net with short delay and

minimal skew. These internal global nets can also be driven from internal logic. If

not used to drive a global net, any of these pins is a user-programmable I/O pin.

The GCK1-GCK8 pins provide the shortest path to the eight Global Low-Skew

Buffers. Any input pad symbol connected directly to the input of a BUFGLS symbol

is automatically placed on one of these pins.

CS1

(Spartan-XL)

I

I/O

During Express configuration, CS1 is used as a serial-enable signal for

daisy-chaining.

D0-D7

(Spartan-XL)

I

I/O

During Express configuration, these eight input pins receive configuration data.

After configuration, they are user-programmable I/O pins.

DIN

I

I/O

During Slave Serial or Master Serial configuration, DIN is the serial configuration

data input receiving data on the rising edge of CCLK. After configuration, DIN is a

user-programmable I/O pin.

DOUT

O

I/O

During Slave Serial or Master Serial configuration, DOUT is the serial

configuration data output that can drive the DIN of daisy-chained slave FPGAs.

DOUT data changes on the falling edge of CCLK, one-and-a-half CCLK periods

after it was received at the DIN input.

In Spartan-XL family Express mode, DOUT is the status output that can drive the

CS1 of daisy-chained FPGAs, to enable and disable downstream devices.

After configuration, DOUT is a user-programmable I/O pin.

Unrestricted User-Programmable I/O Pins

I/O

Weak

Pull-up

I/O

These pins can be configured to be input and/or output after configuration is

completed. Before configuration is completed, these pins have an internal

high-value pull-up resistor network that defines the logic level as High.

Table 18: Pin Descriptions (Continued)

Pin Name

I/O

During

Config.

I/O After

Config.

Pin Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 65801-053LF | CLINCHER RECEPTACLE ASSY GOLD |

| IDT70V3379S4BCG | IC SRAM 576KBIT 4NS 256BGA |

| KMPC8555PXAQF | IC MPU POWERQUICC III 783-FCPBGA |

| KMPC8555PXAPF | IC MPU POWERQUICC III 783-FCPBGA |

| IDT70V3379S4BC | IC SRAM 576KBIT 4NS 256BGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCS20XL-5TQ144I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-5TQ208C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-5TQ208I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-5TQ240C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-5TQ240I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。