- 您現在的位置:買賣IC網 > PDF目錄372886 > XCS05XL-3PC240I (Xilinx, Inc.) Spartan and Spartan-XL Families Field Programmable Gate Arrays PDF資料下載

參數資料

| 型號: | XCS05XL-3PC240I |

| 廠商: | Xilinx, Inc. |

| 英文描述: | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| 中文描述: | 斯巴達和Spartan - xL的家庭現場可編程門陣列 |

| 文件頁數: | 33/66頁 |

| 文件大小: | 809K |

| 代理商: | XCS05XL-3PC240I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁當前第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁

R

DS060 (v1.5) March 2, 2000

Powered by ICminer.com Electronic-Library Service CopyRight 2003

4-33

Spartan and Spartan-XL Families Field Programmable Gate Arrays

Therefore, the specification only applies to the six clock

cycles prior to and including any start bit, including the

clocks before the first start bit in the Readback data stream.

At other times, the frame data is already in the register and

the register is not dynamic. Thus, it can be shifted out just

like a regular shift register.

The user must precisely calculate the location of the Read-

back data relative to the frame. The system must keep track

of the position within a data frame, and disable interrupts

before frame boundaries. Frame lengths and data formats

are listed in

Table 16

and

Table 17

.

Readback with the XChecker Cable

The XChecker Universal Download/Readback Cable and

Logic Probe uses the readback feature for bitstream verifi-

cation. It can also display selected internal signals on the

computer screen, acting as a low-cost in-circuit emulator.

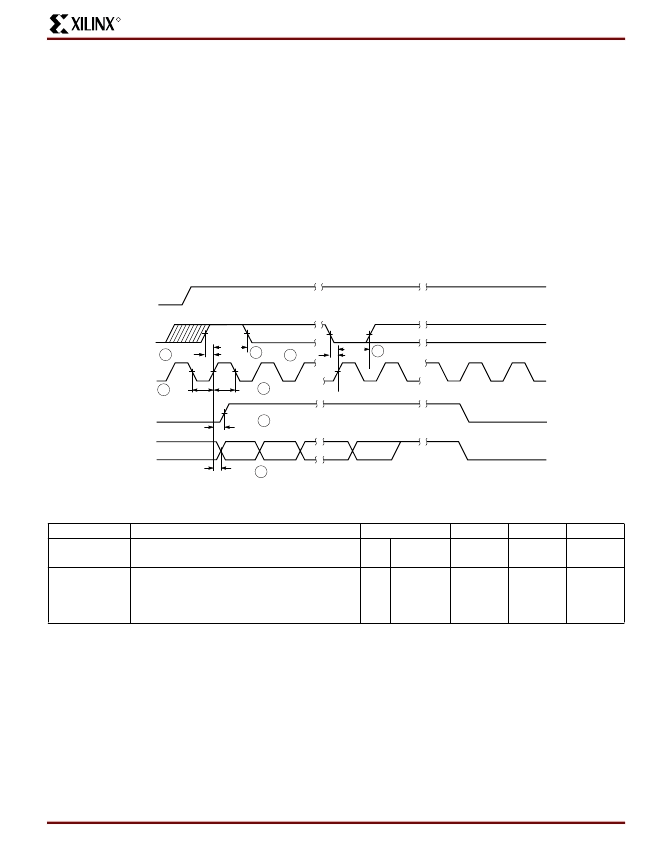

Readback Switching Characteristic Guidelines

Testing of the switching parameters is modeled after testing

methods specified by MIL-M-38510/605. All devices are

100% functionally tested. Internal timing parameters are

not measured directly. They are derived from benchmark

timing patterns that are taken at device introduction, prior to

any process improvements.

The following guidelines reflect worst-case values over the

recommended operating conditions.

Note 1:

Note 2:

Timing parameters apply to all speed grades.

If rdbk.TRIG is High prior to Finished, Finished will trigger the first Readback.

RTRC

T

RCRT

T

RCRT

T

2

2

RCL

T

4

RCRR

T

6

RCH

T

5

RCRD

T

7

DUMMY

DUMMY

rdbk.DATA

rdbk.RIP

rdclk.I

rdbk.TRIG

Finished

Internal Net

VALID

X1790

VALID

1

RTRC

T

1

Spartan and Spartan-XL Readback

Description

rdbk.TRIG

rdbk.TRIG setup to initiate and abort Readback

rdbk.TRIG hold to initiate and abort Readback

rdclk.1

rdbk.DATA delay

rdbk.RIP delay

High time

Low time

Symbol

T

RTRC

T

RCRT

T

RCRD

T

RCRR

T

RCH

T

RCL

Min

200

50

-

-

250

250

Max

-

-

250

250

500

500

Units

ns

ns

ns

ns

ns

ns

1

2

7

6

5

4

相關PDF資料 |

PDF描述 |

|---|---|

| XCS05XL-3PC256C | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-3PC256I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-3PC280C | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-3PC280I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-3PC84C | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

相關代理商/技術參數 |

參數描述 |

|---|---|

| XCS05XL-3PC256C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-3PC256I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-3PC280C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-3PC280I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-3PC84C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL FPGA |

發(fā)布緊急采購,3分鐘左右您將得到回復。