- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄372877 > XC95288-15BG352C Flash Complex PLD PDF資料下載

參數(shù)資料

| 型號(hào): | XC95288-15BG352C |

| 英文描述: | Flash Complex PLD |

| 中文描述: | 閃光復(fù)雜可編程邏輯器件 |

| 文件頁(yè)數(shù): | 15/16頁(yè) |

| 文件大小: | 133K |

| 代理商: | XC95288-15BG352C |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)當(dāng)前第15頁(yè)第16頁(yè)

R

September 15, 1999 (Version 5.0)

15

XC9500 In-System Programmable CPLD Family

5

If the device is in the erased state (before any user pattern

is programmed), the device outputs remain disabled with

the IOB pull-up resistors enabled. The JTAG pins are

enabled to allow the device to be programmed at any time.

If the device is programmed, the device inputs and outputs

take on their configured states for normal operation. The

JTAG pins are enabled to allow device erasure or bound-

ary-scan tests at any time.

Development System Support

The XC9500 CPLD family is fully supported by the develop-

ment systems available from Xilinx and the Xilinx Alliance

Program vendors.

The designer can create the design using ABEL, schemat-

ics, equations, VHDL, or Verilog in a variety of software

front-end tools. The development system can be used to

implement the design and generate a JEDEC bitmap which

can be used to program the XC9500 device. Each develop-

ment system includes JTAG download software that can be

used to program the devices via the standard JTAG inter-

face and a download cable.

FastFLASH Technology

An advanced CMOS Flash process is used to fabricate all

XC9500 devices. Specifically developed for Xilinx in-system pro-

grammable CPLDs, the FastFLASH process provides high

performance logic capability, fast programming times, and

endurance of 10,000 program/erase cycles.

Note:

1. S = the logic span of the function, as defined in the text.

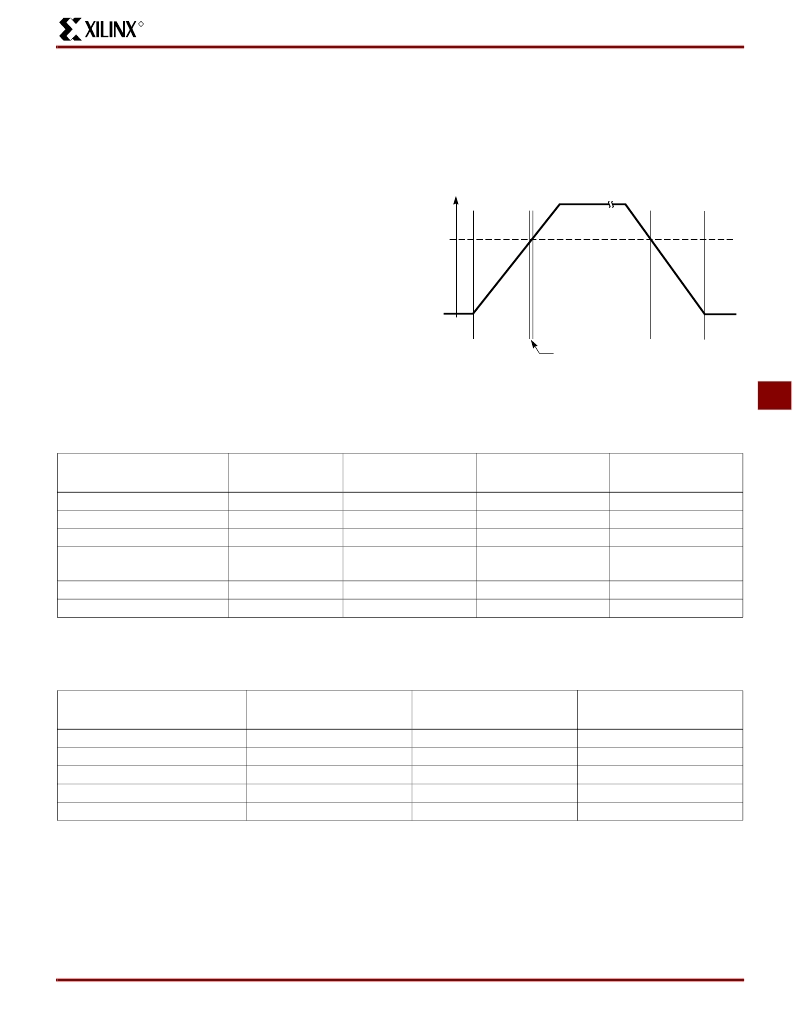

Figure 16: Device Behavior During Power-up

V

CCINT

No

Power

3.8 V

(Typ)

0 V

No

Power

Quiescent

State

Quiescent

State

User Operation

Initialization of User Registers

X5904

Table 4: Timing Model Parameters

Description

Parameter

Product Term

Allocator

1

+ t

PTA

*

S

+ t

PTA

*

S

–

+ t

PTA

*

S

Macrocell

Low-Power Setting

+ t

LP

+ t

LP

–

+ t

LP

Output Slew-Limited

Setting

+ t

SLEW

–

+ t

SLEW

–

Propagation Delay

Global Clock Setup Time

Global Clock-to-output

Product Term Clock Setup

Time

Product Term Clock-to-output

Internal System Cycle Period

t

PD

t

SU

t

CO

t

PSU

t

PCO

t

SYSTEM

–

–

+ t

SLEW

–

+ t

PTA

*

S

+ t

LP

Table 5: XC9500 Device Characteristics

Device

Circuitry

Quiescent

State

Enabled

Disabled

Disabled

Disabled

Disabled

Erased Device

Operation

Enabled

Disabled

Disabled

Disabled

Enabled

Valid User

Operation

Disabled

As Configured

As Configured

As Configured

Enabled

IOB Pull-up Resistors

Device Outputs

Device Inputs and Clocks

Function Block

JTAG Controller

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC95288-15BG352I | Flash Complex PLD |

| XC95288-15HQ208C | Flash Complex PLD |

| XC95288-15HQ208I | Flash Complex PLD |

| XC95288-20BG352C | Flash Complex PLD |

| XC95288XL-6BG352C | Flash Complex PLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC95288-15BG352I | 功能描述:IC CPLD 288 MCELL I-TEMP 352-BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - CPLD(復(fù)雜可編程邏輯器件) 系列:XC9500 標(biāo)準(zhǔn)包裝:24 系列:CoolRunner II 可編程類型:系統(tǒng)內(nèi)可編程 最大延遲時(shí)間 tpd(1):7.1ns 電壓電源 - 內(nèi)部:1.7 V ~ 1.9 V 邏輯元件/邏輯塊數(shù)目:24 宏單元數(shù):384 門(mén)數(shù):9000 輸入/輸出數(shù):173 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:208-BFQFP 供應(yīng)商設(shè)備封裝:208-PQFP(28x28) 包裝:托盤(pán) |

| XC95288-15BGG352C | 制造商:Xilinx 功能描述:XILINX XC95288-15BGG352C CPLD - Trays 制造商:Xilinx 功能描述:Xilinx XC95288-15BGG352C CPLD |

| XC95288-15BGG352I | 制造商:Xilinx 功能描述:XILINX XC95288-15BGG352I CPLD - Trays 制造商:Xilinx 功能描述:Xilinx XC95288-15BGG352I CPLD |

| XC95288-15HQ208C | 功能描述:IC CPLD SPEED GRADE 208-HQFP/COM RoHS:否 類別:集成電路 (IC) >> 嵌入式 - CPLD(復(fù)雜可編程邏輯器件) 系列:XC9500 標(biāo)準(zhǔn)包裝:24 系列:CoolRunner II 可編程類型:系統(tǒng)內(nèi)可編程 最大延遲時(shí)間 tpd(1):7.1ns 電壓電源 - 內(nèi)部:1.7 V ~ 1.9 V 邏輯元件/邏輯塊數(shù)目:24 宏單元數(shù):384 門(mén)數(shù):9000 輸入/輸出數(shù):173 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:208-BFQFP 供應(yīng)商設(shè)備封裝:208-PQFP(28x28) 包裝:托盤(pán) |

| XC9528815HQ208I | 制造商:XILINX 功能描述:* |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。