- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄225573 > XC7K420T-1FFG901E (XILINX INC) FPGA, PBGA900 PDF資料下載

參數(shù)資料

| 型號: | XC7K420T-1FFG901E |

| 廠商: | XILINX INC |

| 元件分類: | FPGA |

| 英文描述: | FPGA, PBGA900 |

| 封裝: | LEAD FREE, FBGA-900 |

| 文件頁數(shù): | 24/50頁 |

| 文件大小: | 1218K |

| 代理商: | XC7K420T-1FFG901E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁

Kintex-7 FPGAs Data Sheet: DC and Switching Characteristics

DS182 (v1.1) April 1, 2011

Advance Product Specification

30

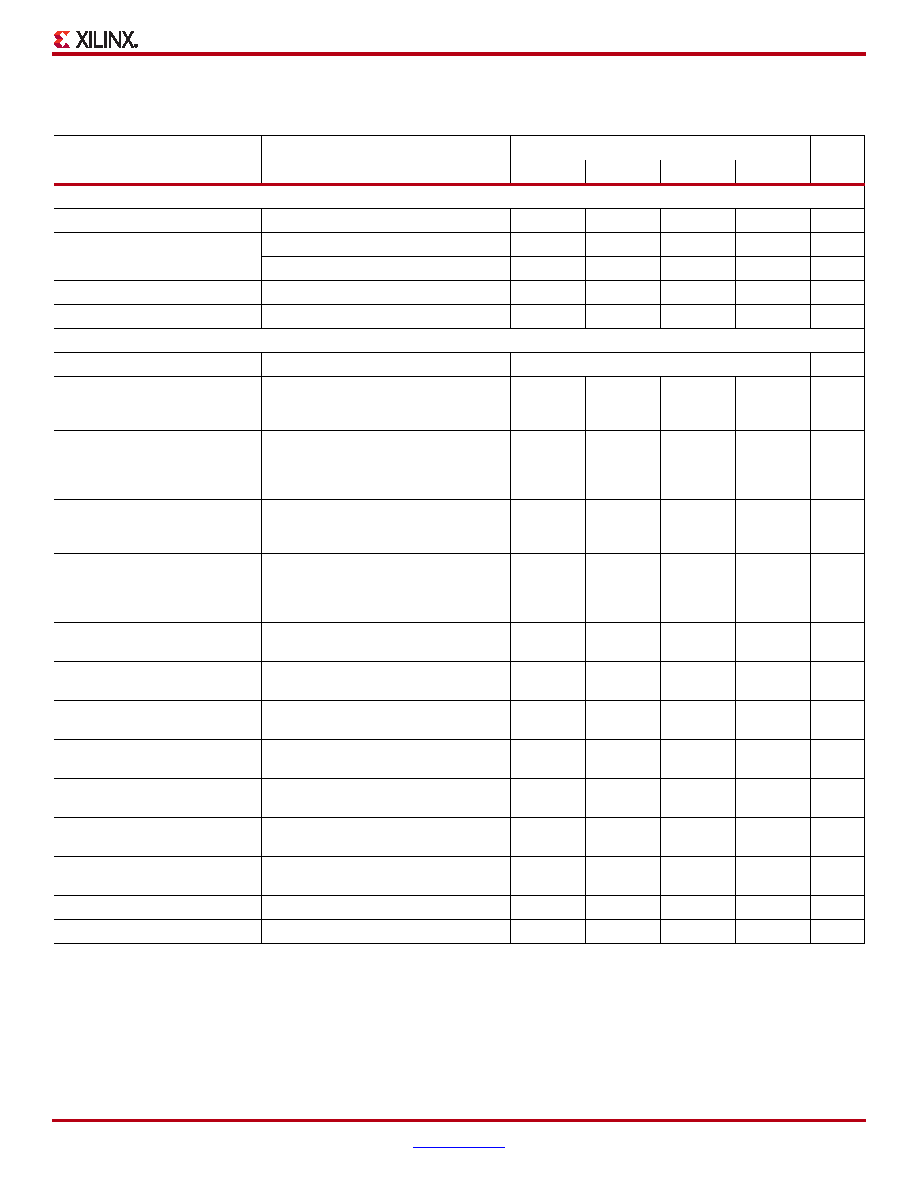

Input/Output Delay Switching Characteristics

Table 34: Input/Output Delay Switching Characteristics

Symbol

Description

Speed Grade

Units

-3

-2

-1

-1L

IDELAYCTRL

TDLYCCO_RDY

Reset to Ready for IDELAYCTRL

3.25

s

FIDELAYCTRL_REF

Attribute REFCLK frequency = 200.0(1)

200

MHz

Attribute REFCLK frequency = 300.0(1)

300

N/A

MHz

IDELAYCTRL_REF_PRECISION

REFCLK precision

±10

MHz

TIDELAYCTRL_RPW

Minimum Reset pulse width

52.5

ns

IDELAY/ODELAY

TIDELAYRESOLUTION

IDELAY/ODELAY chain delay resolution

1/(32 x 2 x FREF)ps

TIDELAYPAT_JIT_CLOCK

Pattern dependent period jitter in delay

chain for clock pattern.

(HP I/O banks only)(2)

000

ps

per tap

TIDELAYPAT_JIT_DATA

Pattern dependent period jitter in delay

chain for random data pattern

(PRBS 23)

(HP I/O banks only)(2)

±5

ps

per tap

TIDELAYPAT_JIT_CLOCK

Pattern dependent period jitter in delay

chain for clock pattern.

(HR I/O banks only)(2)

000

ps

per tap

TIDELAYPAT_JIT_DATA

Pattern dependent period jitter in delay

chain for random data pattern

(PRBS 23)

(HR I/O banks only)(2)

±9

ps

per tap

TIDELAY_CLK_MAX/

TODELAY_CLK_MAX

Maximum frequency of CLK input to

IDELAY/ODELAY

800

710

MHz

TIDCCK_CE / TIDCKC_CE

CE pin Setup/Hold with respect to C for

IDELAY

–0.02/

0.21

–0.02/

0.24

–0.02/

0.30

ns

TODCCK_CE / TODCKC_CE

CE pin Setup/Hold with respect to C for

ODELAY

–0.02/

0.21

–0.02/

0.25

–0.02/

0.30

ns

TIDCCK_INC/ TIDCKC_INC

INC pin Setup/Hold with respect to C for

IDELAY

0.10/

0.24

0.11/

0.28

0.12/

0.34

ns

TODCCK_INC/ TODCKC_INC

INC pin Setup/Hold with respect to C for

ODELAY

0.11/

0.24

0.11/

0.28

0.12/

0.34

ns

TIDCCK_RST/ TIDCKC_RST

RST pin Setup/Hold with respect to C for

IDELAY

0.10/

0.26

0.12/

0.31

0.14/

0.38

ns

TODCCK_RST/ TODCKC_RST

RST pin Setup/Hold with respect to C for

ODELAY

0.10/

0.27

0.12/

0.32

0.15/

0.38

ns

TIDDO_IDATAIN

Propagation delay through IDELAY

Note 2

ps

TODDO_ODATAIN

Propagation delay through ODELAY

Note 2

ps

Notes:

1.

Average Tap Delay at 200 MHz = 78 ps, at 300 MHz = 52 ps.

2.

Delay depends on IDELAY/ODELAY tap setting. See TRACE report for actual values.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC7K420T-1FFG901I | FPGA, PBGA900 |

| XC7K420T-1LFFG1156C | FPGA, PBGA1156 |

| XC7K420T-1LFFG1156E | FPGA, PBGA1156 |

| XC7K420T-1LFFG1156I | FPGA, PBGA1156 |

| XC7K420T-1LFFG901C | FPGA, PBGA900 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC7K420T-1FFG901I | 制造商:Xilinx 功能描述:KINTEX-7 - Trays 制造商:Xilinx 功能描述:IC FPGA 380 I/O 901FCBGA 制造商:Xilinx 功能描述:IC FPGA 420K KINTEX-7 901FBGA |

| XC7K420T-2FF1156C | 制造商:Xilinx 功能描述:KINTEX-7 - Trays 制造商:Xilinx 功能描述:IC FPGA 400 I/O 1156FCBGA |

| XC7K420T-2FF1156I | 制造商:Xilinx 功能描述:KINTEX-7 - Trays 制造商:Xilinx 功能描述:IC FPGA 400 I/O 1156FCBGA |

| XC7K420T-2FF901C | 制造商:Xilinx 功能描述:KINTEX-7 - Trays 制造商:Xilinx 功能描述:IC FPGA 420K KINTEX-7 901FBGA |

| XC7K420T-2FF901I | 制造商:Xilinx 功能描述:KINTEX-7 - Trays 制造商:Xilinx 功能描述:IC FPGA 380 I/O 901FCBGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。