- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4159 > XC4013E-1HQ208C (Xilinx Inc)IC FPGA C-TEMP 5V 1SPD 208-HQFP PDF資料下載

參數(shù)資料

| 型號(hào): | XC4013E-1HQ208C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 32/68頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA C-TEMP 5V 1SPD 208-HQFP |

| 產(chǎn)品變化通告: | XC1700 PROMs,XC5200,HQ,SCD Parts Discontinuation 19/Jul/2010 |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | XC4000E/X |

| LAB/CLB數(shù): | 576 |

| 邏輯元件/單元數(shù): | 1368 |

| RAM 位總計(jì): | 18432 |

| 輸入/輸出數(shù): | 160 |

| 門數(shù): | 13000 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 208-BFQFP 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 208-PQFP(28x28) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

R

XC4000E and XC4000X Series Field Programmable Gate Arrays

6-42

May 14, 1999 (Version 1.6)

Boundary Scan

The ‘bed of nails’ has been the traditional method of testing

electronic assemblies. This approach has become less

appropriate, due to closer pin spacing and more sophisti-

cated assembly methods like surface-mount technology

and multi-layer boards. The IEEE Boundary Scan Standard

1149.1 was developed to facilitate board-level testing of

electronic assemblies. Design and test engineers can

imbed a standard test logic structure in their device to

achieve high fault coverage for I/O and internal logic. This

structure is easily implemented with a four-pin interface on

any boundary scan-compatible IC. IEEE 1149.1-compati-

ble devices may be serial daisy-chained together, con-

nected in parallel, or a combination of the two.

The XC4000 Series implements IEEE 1149.1-compatible

BYPASS, PRELOAD/SAMPLE and EXTEST boundary

scan instructions. When the boundary scan conguration

option is selected, three normal user I/O pins become ded-

icated inputs for these functions. Another user output pin

becomes the dedicated boundary scan output. The details

of how to enable this circuitry are covered later in this sec-

tion.

By exercising these input signals, the user can serially load

commands and data into these devices to control the driv-

ing of their outputs and to examine their inputs. This

method is an improvement over bed-of-nails testing. It

avoids the need to over-drive device outputs, and it reduces

the user interface to four pins. An optional fth pin, a reset

for the control logic, is described in the standard but is not

implemented in Xilinx devices.

The dedicated on-chip logic implementing the IEEE 1149.1

functions includes a 16-state machine, an instruction regis-

ter and a number of data registers. The functional details

can be found in the IEEE 1149.1 specication and are also

discussed in the Xilinx application note XAPP 017: “

Bound-

ary Scan in XC4000 Devices.”

Figure 40 on page 43 shows a simplied block diagram of

the XC4000E Input/Output Block with boundary scan

implemented. XC4000X boundary scan logic is identical.

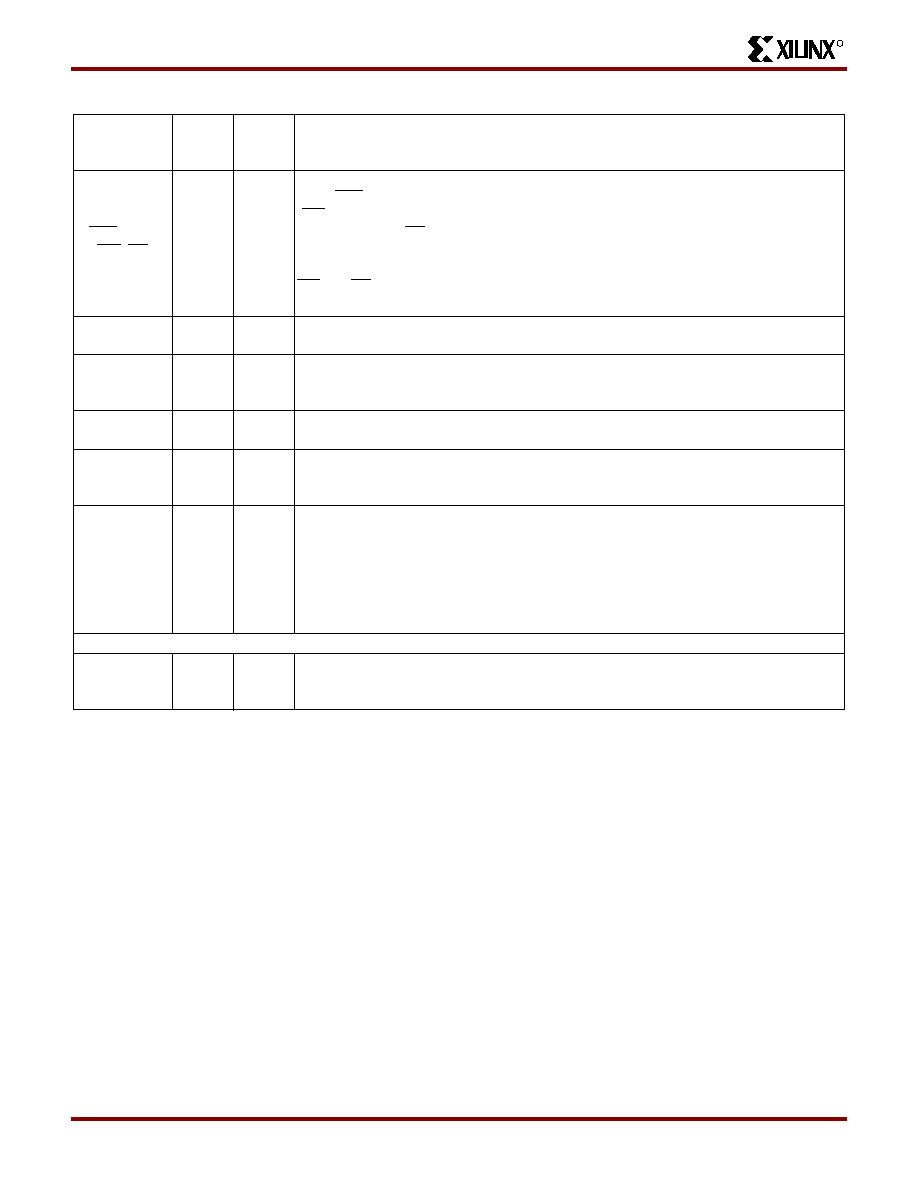

CS0, CS1,

WS, RS

I

I/O

These four inputs are used in Asynchronous Peripheral mode. The chip is selected

when CS0 is Low and CS1 is High. While the chip is selected, a Low on Write Strobe

(WS) loads the data present on the D0 - D7 inputs into the internal data buffer. A Low

on Read Strobe (RS) changes D7 into a status output — High if Ready, Low if Busy —

and drives D0 - D6 High.

In Express mode, CS1 is used as a serial-enable signal for daisy-chaining.

WS and RS should be mutually exclusive, but if both are Low simultaneously, the Write

Strobe overrides. After configuration, these are user-programmable I/O pins.

A0 - A17

O

I/O

During Master Parallel configuration, these 18 output pins address the configuration

EPROM. After configuration, they are user-programmable I/O pins.

A18 - A21

(XC4003XL to

XC4085XL)

O

I/O

During Master Parallel configuration with an XC4000X master, these 4 output pins add

4 more bits to address the configuration EPROM. After configuration, they are user-pro-

grammable I/O pins. (See Master Parallel Configuration section for additional details.)

D0 - D7

I

I/O

During Master Parallel and Peripheral configuration, these eight input pins receive con-

figuration data. After configuration, they are user-programmable I/O pins.

DIN

I

I/O

During Slave Serial or Master Serial configuration, DIN is the serial configuration data

input receiving data on the rising edge of CCLK. During Parallel configuration, DIN is

the D0 input. After configuration, DIN is a user-programmable I/O pin.

DOUT

O

I/O

During configuration in any mode but Express mode, DOUT is the serial configuration

data output that can drive the DIN of daisy-chained slave FPGAs. DOUT data changes

on the falling edge of CCLK, one-and-a-half CCLK periods after it was received at the

DIN input.

In Express modefor XC4000E and XC4000X only, DOUT is the status output that can

drive the CS1 of daisy-chained FPGAs, to enable and disable downstream devices.

After configuration, DOUT is a user-programmable I/O pin.

Unrestricted User-Programmable I/O Pins

I/O

Weak

Pull-up

I/O

These pins can be configured to be input and/or output after configuration is completed.

Before configuration is completed, these pins have an internal high-value pull-up resis-

tor (25 k

- 100 k) that defines the logic level as High.

Table 16: Pin Descriptions (Continued)

Pin Name

I/O

During

Cong.

I/O

After

Cong.

Pin Description

Product Obsolete or Under Obsolescence

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC4013E-1BG225C | IC FPGA C-TEMP 5V 1SPD 225-PBGA |

| AMC44DRTN-S734 | CONN EDGECARD 88POS DIP .100 SLD |

| 65801-009LF | CONN RCPT 9POS 2.54MM VERT TIN |

| AMC44DRTH-S734 | CONN EDGECARD 88POS DIP .100 SLD |

| AMC44DREN-S734 | CONN EDGECARD 88POS .100 EYELET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC4013E-1HQ208I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC4013E-1HQ240C | 功能描述:IC FPGA C-TEMP 5V 1SPD 240-HQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:XC4000E/X 標(biāo)準(zhǔn)包裝:1 系列:Kintex-7 LAB/CLB數(shù):25475 邏輯元件/單元數(shù):326080 RAM 位總計(jì):16404480 輸入/輸出數(shù):350 門數(shù):- 電源電壓:0.97 V ~ 1.03 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:900-BBGA,F(xiàn)CBGA 供應(yīng)商設(shè)備封裝:900-FCBGA(31x31) 其它名稱:122-1789 |

| XC4013E-1HQ240I | 制造商:XILINX 制造商全稱:XILINX 功能描述:XC4000E and XC4000X Series Field Programmable Gate Arrays |

| XC4013E-1HQ240M | 制造商:XILINX 制造商全稱:XILINX 功能描述:XC4000E and XC4000X Series Field Programmable Gate Arrays |

| XC4013E-1MQ240C | 制造商:XILINX 制造商全稱:XILINX 功能描述:XC4000E and XC4000X Series Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。