- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄300144 > XC4000XLASERIES (Xilinx, Inc.) Field Programmable Gate Arrays PDF資料下載

參數(shù)資料

| 型號(hào): | XC4000XLASERIES |

| 廠商: | Xilinx, Inc. |

| 英文描述: | Field Programmable Gate Arrays |

| 中文描述: | 現(xiàn)場(chǎng)可編程門(mén)陣列 |

| 文件頁(yè)數(shù): | 2/14頁(yè) |

| 文件大小: | 142K |

| 代理商: | XC4000XLASERIES |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)

R

XC4000XLA/XV Field Programmable Gate Arrays

6-166

DS015 (v1.3) October 18, 1999 - Product Specication

Data Stream Format

The data stream (“bitstream”) format is identical for all

serial

conguration

modes,

but

different

for

the

4000XLA/XV Express mode. In Express mode, the device

becomes active when DONE goes High, therefore no

length count is required. Additionally, CRC error checking is

not supported in Express mode. The data stream format is

shown in Table 9. Express mode data is shown with D0 at

the left and D7 at the right.

The conguration data stream begins with two bytes of

eight ones each, a preamble code of one byte, followed by

three bytes of eight ones each, and nally an end-of-

header eld check byte. This header of seven bytes is fol-

lowed by the actual conguration data in frames. The

length and number of frames depends on the device type.

Each frame begins with a start eld and ends with an

end-of-frame eld check byte. In all cases, additional

start-up bytes of data are required to provide six, or more,

clocks for the start-up sequence at the end of conguration.

Long daisy chains require additional startup bytes to shift

the last data through the chain. All startup bytes are

don’t-cares; these bytes are not included in bitstreams cre-

ated by the Xilinx software.

A selection of CRC or non-CRC error checking is allowed

by the bitstream generation software. The 4000XLA

Express mode only supports non-CRC error checking. The

non-CRC

error

checking

tests

for

a

designated

end-of-frame eld check byte for each frame. non-CRC

error checking tests for a designated end-of-frame eld

check byte for each frame.

LEGEND:

Detection of an error results in the suspension of data load-

ing and the pulling down of the INIT pin. The user must

detect INIT and initialize a new conguration by pulsing the

PROGRAM pin Low or cycling VCC.

Note: CS1

must remain High throughout loading of the conguration data stream. In the pseudo daisy chain of Figure 5, the 7 byte

data stream header is loaded into all devices simultaneously. Each device’s data frames are then loaded in turn when its

CS1 pin is driven High by the DOUT of the preceding device in the chain.

99012600

BYTE

0

CCLK

1

2

3

INIT

T

DC

T

CD

T

IC

D0-D7

DOUT

CS1

First

FPGA

BYTE

1

BYTE

2

BYTE

3

First FPGA Filled

BYTE

4

BYTE

5

BYTE

6

Header

Header Loaded

CS1

Second

FPGA

CS1 all

downstream

FPGAs

Byte A is first frame byte for first FPGA

Byte B is last frame byte for first FPGA

Byte C is first frame byte for second FPGA

BYTE

A

BYTE

C

BYTE

B

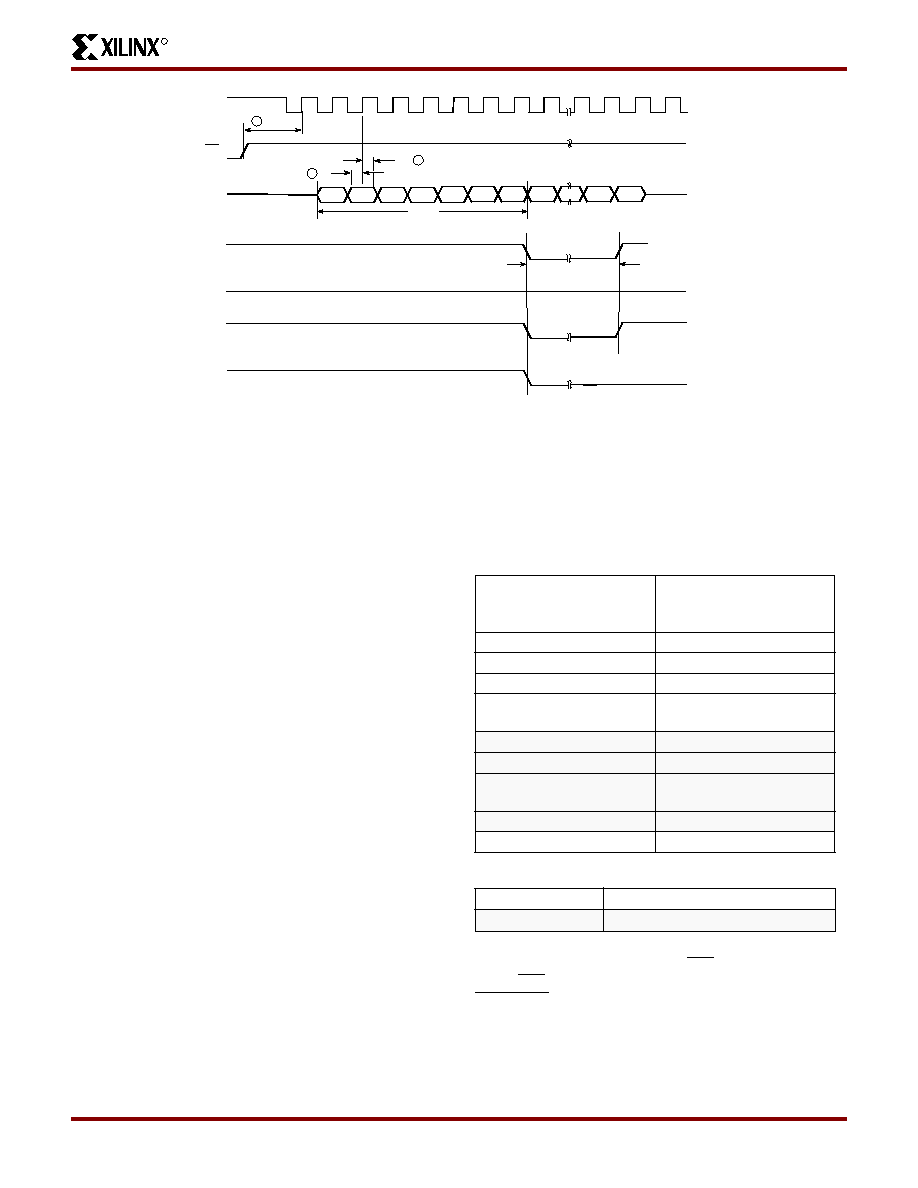

Figure 6: Express Mode Conguration Switching Waveforms

Table 9: 4000XLA/XV Express Mode Data Stream

Format

Data Type

Express Mode

(D0-D7)

(4000XLA only)

Fill Byte

FFFFh

Preamble Code

11110010b

Fill Byte

FFFFFFh

End-of-Header

Field Check Byte

11010010b

Start Field

11111110b

Data Frame

DATA(n-1:0)

End-of-Frame

Field Check Byte

11010010b

Extend Write Cycle

FFD2FFFFFFh

Start-Up Bytes

FFFFFFFFFFFFh

Unshaded

Once per data stream

Light

Once per data frame

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC4013E-1CB240M | Programmable Gate Arrays |

| XC4013E-1HG240C | Programmable Gate Arrays |

| XC4013E-3BG240M | XC4000E and XC4000X Series Field Programmable Gate Arrays |

| XC4013E-1VQ240M | XC4000E and XC4000X Series Field Programmable Gate Arrays |

| XC4013E-2BG240C | XC4000E and XC4000X Series Field Programmable Gate Arrays |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC4000XSERIES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Programmable Gate Arrays |

| XC4000XV | 制造商:XILINX 制造商全稱:XILINX 功能描述:XC4000XLA/XV Field Programmable Gate Arrays |

| XC4000XVSERIES | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC4002 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| XC4002A | 制造商:XILINX 制造商全稱:XILINX 功能描述:Logic Cell Array Families |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。