- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4176 > XC3064A-7PC84C (Xilinx Inc)IC LOGIC CL ARRAY 6400GAT 84PLCC PDF資料下載

參數(shù)資料

| 型號: | XC3064A-7PC84C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 67/76頁 |

| 文件大小: | 0K |

| 描述: | IC LOGIC CL ARRAY 6400GAT 84PLCC |

| 產(chǎn)品變化通告: | Product Discontinuation 27/Apr/2010 |

| 標準包裝: | 1 |

| 系列: | XC3000A/L |

| LAB/CLB數(shù): | 224 |

| RAM 位總計: | 46064 |

| 輸入/輸出數(shù): | 70 |

| 門數(shù): | 4500 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 84-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 84-PLCC |

| 其它名稱: | 122-1029 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁當前第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

R

November 9, 1998 (Version 3.1)

7-9

XC3000 Series Field Programmable Gate Arrays

7

Configurable Logic Block

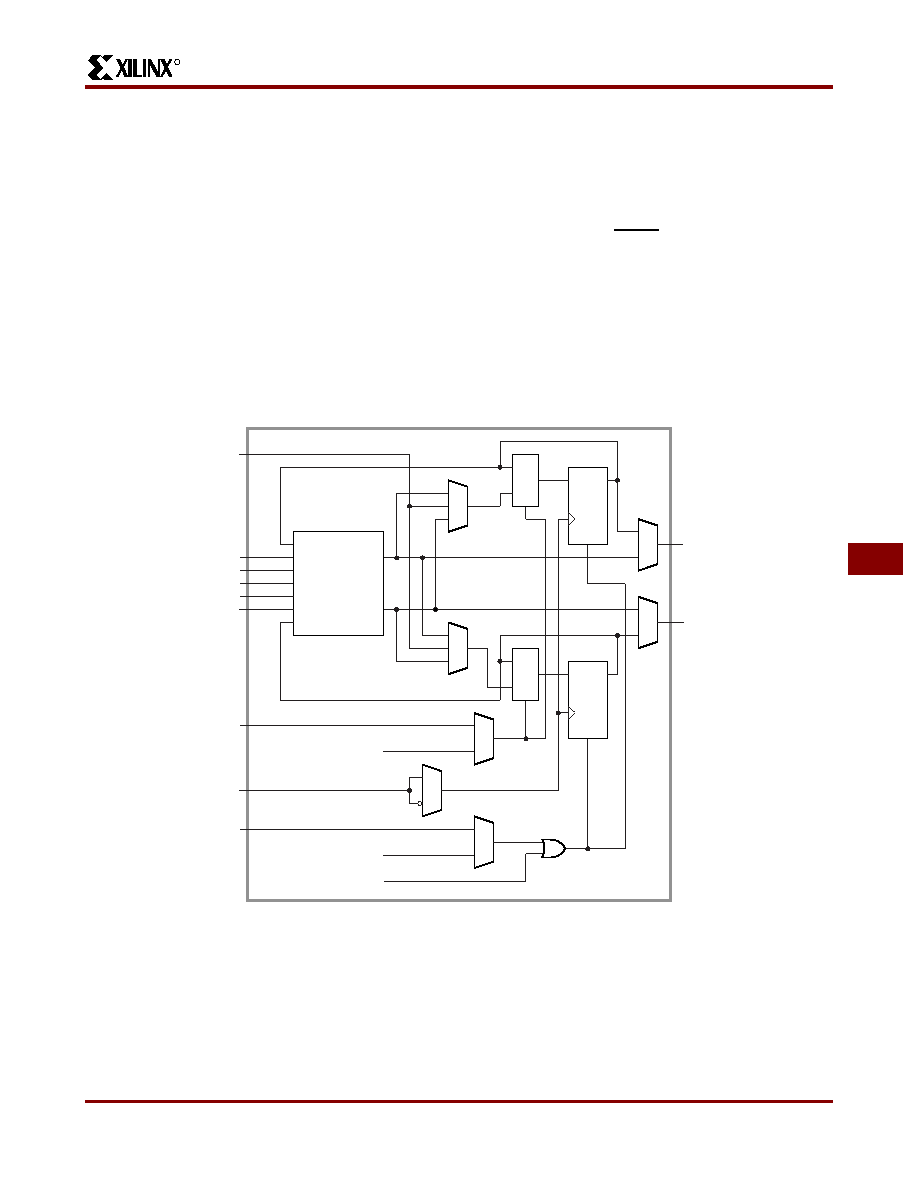

The array of CLBs provides the functional elements from

which the user’s logic is constructed. The logic blocks are

arranged in a matrix within the perimeter of IOBs. For

example, the XC3020A has 64 such blocks arranged in 8

rows and 8 columns. The development system is used to

compile the configuration data which is to be loaded into

the internal configuration memory to define the operation

and interconnection of each block. User definition of CLBs

and their interconnecting networks may be done by auto-

matic translation from a schematic-capture logic diagram or

optionally by installing library or user macros.

Each CLB has a combinatorial logic section, two flip-flops,

and an internal control section. See Figure 5. There are:

five logic inputs (A, B, C, D and E); a common clock input

(K); an asynchronous direct RESET input (RD); and an

enable clock (EC). All may be driven from the interconnect

resources adjacent to the blocks. Each CLB also has two

outputs (X and Y) which may drive interconnect networks.

Data input for either flip-flop within a CLB is supplied from

the function F or G outputs of the combinatorial logic, or the

block input, DI. Both flip-flops in each CLB share the asyn-

chronous RD which, when enabled and High, is dominant

over clocked inputs. All flip-flops are reset by the

active-Low chip input, RESET, or during the configuration

process. The flip-flops share the enable clock (EC) which,

when Low, recirculates the flip-flops’ present states and

inhibits response to the data-in or combinatorial function

inputs on a CLB. The user may enable these control inputs

and select their sources. The user may also select the

clock net input (K), as well as its active sense within each

CLB. This programmable inversion eliminates the need to

route both phases of a clock signal throughout the device.

Q

COMBINATORIAL

FUNCTION

LOGIC

VARIABLES

D

RD

G

F

DIN

F

G

QX

QY

DIN

F

G

QY

QX

F

Q

D

RD

ENABLE CLOCK

CLOCK

DIRECT

RESET

1 (ENABLE)

A

B

C

D

E

DI

EC

K

RD

Y

X

X3032

0 (INHIBIT)

(GLOBAL RESET)

CLB OUTPUTS

DATA IN

0

1

0

1

MUX

Figure 5: Configurable Logic Block.

Each CLB includes a combinatorial logic section, two flip-flops and a program memory controlled multiplexer selection of

function. It has the following:

-

five logic variable inputs A, B, C, D, and E

-

a direct data in DI

-

an enable clock EC

-

a clock (invertible) K

-

an asynchronous direct RESET RD

-

two outputs X and Y

Product Obsolete or Under Obsolescence

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC3064A-7PQ160C | IC LOGIC CL ARRAY 6400GAT 160PQF |

| ASC49DRYH-S93 | CONN EDGECARD 98POS DIP .100 SLD |

| AMC44DRTI-S13 | CONN EDGECARD 88POS .100 EXTEND |

| AMC44DREI-S13 | CONN EDGECARD 88POS .100 EXTEND |

| FMC18DRES | CONN EDGECARD 36POS .100 EYELET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC3064A-7PC84C0100 | 制造商:Xilinx 功能描述: |

| XC3064A-7PC84I | 制造商:Xilinx 功能描述: 制造商: 功能描述: 制造商:undefined 功能描述: |

| XC3064A-7PG132C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

| XC3064A-7PG132I | 制造商:Xilinx 功能描述: |

| XC3064A-7PP132C | 制造商:Xilinx 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。