- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376449 > X98021L128-3.3 (INTERSIL CORP) 210MHz Triple Video Digitizer with Digital PLL PDF資料下載

參數(shù)資料

| 型號(hào): | X98021L128-3.3 |

| 廠商: | INTERSIL CORP |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | 210MHz Triple Video Digitizer with Digital PLL |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP128 |

| 封裝: | 14 X 20 MM, MS-022, MQFP-128 |

| 文件頁(yè)數(shù): | 20/29頁(yè) |

| 文件大小: | 294K |

| 代理商: | X98021L128-3.3 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)

20

FN8219.0

June 2, 2005

Clock Generation

A Digital Phase Lock Loop (DPLL) is employed to generate

the pixel clock frequency. The HSYNC input and the external

XTAL provide a reference frequency to the PLL. The PLL

then generates the pixel clock frequency that is equal to the

incoming HSYNC frequency times the HTOTAL value

programmed into registers 0x0E and 0x0F.

The stability of the clock is very important and correlates

directly with the quality of the image. During each pixel time

transition, there is a small window where the signal is

slewing from the old pixel amplitude and settling to the new

pixel value. At higher frequencies, the pixel time transitions

at a faster rate, which makes the stable pixel time even

smaller. Any jitter in the pixel clock reduces the effective

stable pixel time and thus the sample window in which pixel

sampling can be made accurately.

Sampling Phase

The X98021 provides 64 low-jitter phase choices per pixel

period, allowing the firmware to precisely select the optimum

sampling point. The sampling phase register is 0x10.

HSYNC Slicer

To further minimize jitter, the HSYNC inputs are treated as

analog signals, and brought into a precision slicer block with

thresholds programmable in 400mV steps with 240mV of

hysteresis, and a subsequent digital glitch filter that ignores

any HSYNC transitions within 100ns of the initial transition.

This processing greatly increases the AFE’s rejection of

ringing and reflections on the HSYNC line and allows the

AFE to perform well even with pathological HSYNC signals.

Voltages given above and in the HSYNC Slicer register

description are with respect to a 3.3V sync signal at the

HSYNC

IN

input pin. To achieve 5V compatibility, a 680

Ω

series resistor should be placed between the HSYNC source

and the HSYNC

IN

input pin. Relative to a 5V input, the

hysteresis will be 240mV*5V/3.3V = 360mV, and the slicer

step size will be 400mV*5V/3.3V = 600mV per step.

The best HSYNC slicer threshold is generally 800mV (001b)

when locking on the rising edge of an HSYNC signal, or 2.4V

(110b) when locking on the falling edge.

SOG Slicer

The SOG input has programmable threshold, 40mV of

hysteresis, and an optional low pass filter than can be used

to remove high frequency video spikes (generated by

overzealous video peaking in a DVD player, for example)

that can cause false SOG triggers. The SOG threshold sets

the comparator threshold relative to the sync tip (the bottom

of the SOG pulse). A good default SOG slicer threshold

setting is 0x16 (hysteresis and low pass filter enabled,

threshold lowered slightly to accommodate weak sync tips).

SYNC Status and Polarity Detection

The SYNC Status register (0x01) and the SYNC Polarity

register (0x02) continuously monitor all 6 sync inputs

(VSYNC

IN

, HSYNC

IN

, and SOG

IN

for each of 2 channels)

and report their status. However, accurate sync activity

detection is always a challenge. Noise and repetitive video

patterns on the Green channel may look like SOG activity

when there actually is no SOG signal, while non-standard

SOG signals and trilevel sync signals may have amplitudes

below the default SOG slicer levels and not be easily

detected. As a consequence, not all of the activity detect bits

in the X980xx are correct under all conditions.

Table 6 shows how to use the SYNC Status register (0x01)

to identify the presence of and type of a sync source. The

firmware should go through the table in the order shown,

stopping at the first entry that matches the activity indicators

in the SYNC Status register.

Final validation of composite sync sources (SOG or

Composite sync on HSYNC) should be done by setting the

Input Configuration register (0x05) to the composite sync

source determined by this table, and confirming that the

CSYNC detect bit is set.

The accuracy of the Trilevel Sync detect bit can be increased

by multiple reads of the Trilevel Sync detect bit. See the

Trilevel Sync Detect

section for more details.

For best SOG operation, the SOG low pass filter (register

0x04[4]) should always be enabled to reject the high

frequency peaking often seen on video signals.

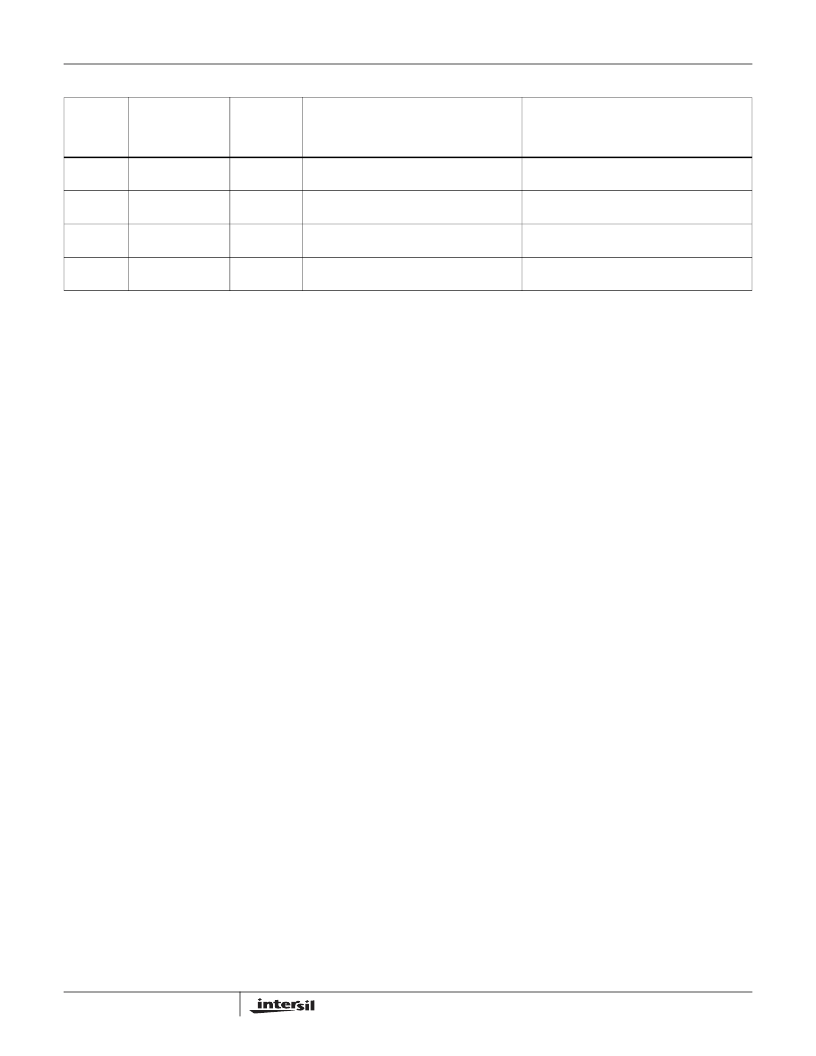

TABLE 5. OFFSET DAC RANGE AND OFFSET DAC ADJUSTMENT

OFFSET

DAC

RANGE

0x0C[0]

10 BIT

OFFSET DAC

RESOLUTION

ABLC

0x17[0]

USER OFFSET CONTROL RESOLUTION

USING

REGISTERS 0x09 - 0x0B ONLY

(8 BIT OFFSET CONTROL)

USER OFFSET CONTROL RESOLUTION

USING

REGISTERS 0x09 - 0x0B AND 0x0C[7:2]

(10 BIT OFFSET CONTROL)

0

0.25 ADC LSBs

(0.68mV)

0

(ABLC on)

1 ADC LSB

(digital offset control)

N/A

1

0.125 ADC LSBs

(0.34mV)

0

(ABLC on)

1 ADC LSB

(digital offset control)

N/A

0

0.25 ADC LSBs

(0.68mV)

1

(ABLC off)

1.0 ADC LSB

(analog offset control)

0.25 ADC LSB

(analog offset control)

1

0.125 ADC LSBs

(0.34mV)

1

(ABLC off)

0.5 ADC LSB

(analog offset control)

0.125 ADC LSB

(analog offset control)

X98021

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X98021L128-3.3-Z | 210MHz Triple Video Digitizer with Digital PLL |

| X98024 | 240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3 | 240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3-Z | 240MHz Triple Video Digitizer with Digital PLL |

| XC145481 | 3 V PCM Codec-Filter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X98024 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:240MHz Triple Video Digitizer with Digital PLL |

| X98024_06 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3-Z | 功能描述:IC TRPL VID DIGITIZER 128MQFP RoHS:是 類別:集成電路 (IC) >> 線性 - 視頻處理 系列:- 標(biāo)準(zhǔn)包裝:250 系列:- 類型:電平移位器 應(yīng)用:LCD 電視機(jī)/監(jiān)控器 安裝類型:表面貼裝 封裝/外殼:28-WFQFN 裸露焊盤(pán) 供應(yīng)商設(shè)備封裝:28-WQFN(4x4)裸露焊盤(pán) 包裝:帶卷 (TR) 其它名稱:296-32523-2TPS65198RUYT-ND |

| X98027 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:PRELIMINARY INFORMATION |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。