- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄376449 > X98021L128-3.3 (INTERSIL CORP) 210MHz Triple Video Digitizer with Digital PLL PDF資料下載

參數(shù)資料

| 型號(hào): | X98021L128-3.3 |

| 廠商: | INTERSIL CORP |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | 210MHz Triple Video Digitizer with Digital PLL |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP128 |

| 封裝: | 14 X 20 MM, MS-022, MQFP-128 |

| 文件頁(yè)數(shù): | 14/29頁(yè) |

| 文件大小: | 294K |

| 代理商: | X98021L128-3.3 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)

14

FN8219.0

June 2, 2005

0x17

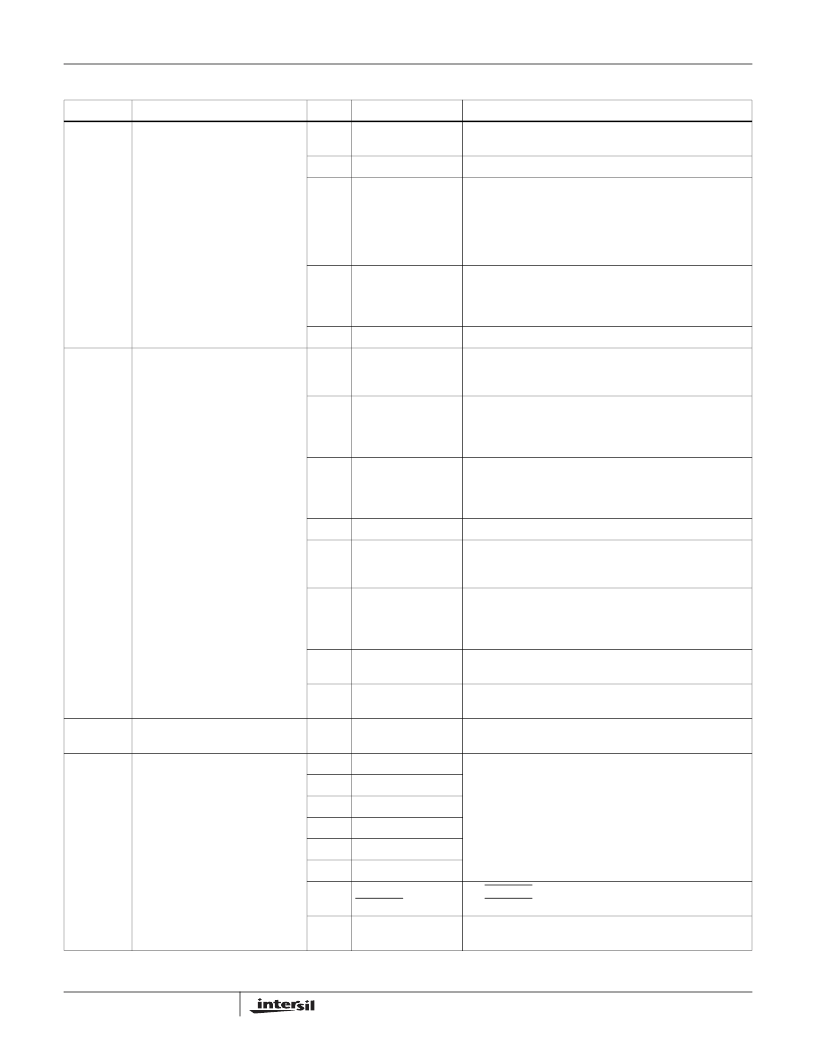

ABLC Configuration (0x40)

0

ABLC disable

0: ABLC enabled (default)

1: ABLC disabled

1

Reserved

Set to 0.

3:2

ABLC pixel width

Number of black pixels averaged every line for ABLC

function

00: 16 pixels [default]

01: 32 pixels

10: 64 pixels

11: 128 pixels

6:4

ABLC bandwidth

ABLC Time constant (lines) = 2

(5+[6:4])

000 = 32 lines

100 = 256 lines (default)

111 = 4096 lines

7

Reserved

Set to 0.

0x18

Output Format (0x00)

0

Bus Width

0: 24 bits: Data output on R

P

, G

P

, B

P

only; R

S

, G

S

, B

S

are all

driven low (default)

1: 48 bits: Data output on R

P

, G

P

, B

P

, R

S

, G

S

, B

S

1

Interleaving

(48 bit mode only)

0: No interleaving: data changes on same edge of DATACLK

(default)

1: Interleaved: Secondary databus data changes on

opposite edge of DATACLK from primary databus

2

Bus Swap

(48 bit mode only)

0: First data byte after trailing edge of HSOUT appears on

R

P

, G

P

, B

P

(default)

1: First data byte after trailing edge of HSOUT appears on

R

S

, G

S

, B

S

(primary and secondary busses are reversed)

3

Reserved

Set to 0.

4

422

(24 bit mode only)

0: Data is formatted as 4:4:4 (RGB, default)

1: Data is decimated to 4:2:2 (YUV), blue channel is driven

low

5

DATACLK

Polarity

0: HS

OUT

, VS

OUT

, and Pixel Data change on falling edge of

DATACLK (default)

1: HS

OUT

, VS

OUT

, and Pixel Data change on rising edge of

DATACLK

6

VSOUT Polarity

0: Active High (default)

1: Active Low

7

HSOUT Polarity

0: Active High (default)

1: Active Low

0x19

HSOUT Width (0x10)

7:0

HSOUT Width

HSOUT width, in pixels. Minimum value is 0x01 for 24 bit

modes, 0x02 for 48 bit modes.

0x1A

Output Signal Disable (0x00)

0

Three-state R

P

[7:0]

0 = Output byte enabled

1 = Output byte three-stated

These bits override all other I/O settings

Output data pins have 58k

Ω

pulldown resistors to GND

D

.

1

Three-state R

S

[7:0]

2

Three-state G

P

[7:0]

3

Three-state G

S

[7:0]

4

Three-state B

P

[7:0]

5

Three-state B

S

[7:0]

6

Three-state

DATACLK

0 = DATACLK enabled

1 = DATACLK three-stated

7

Three-state

DATACLK

0 = DATACLK enabled

1 = DATACLK three-stated

Register Listing

(Continued)

ADDRESS

REGISTER (DEFAULT VALUE)

BIT(s)

FUNCTION NAME

DESCRIPTION

X98021

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X98021L128-3.3-Z | 210MHz Triple Video Digitizer with Digital PLL |

| X98024 | 240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3 | 240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3-Z | 240MHz Triple Video Digitizer with Digital PLL |

| XC145481 | 3 V PCM Codec-Filter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X98024 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:240MHz Triple Video Digitizer with Digital PLL |

| X98024_06 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3-Z | 功能描述:IC TRPL VID DIGITIZER 128MQFP RoHS:是 類別:集成電路 (IC) >> 線性 - 視頻處理 系列:- 標(biāo)準(zhǔn)包裝:250 系列:- 類型:電平移位器 應(yīng)用:LCD 電視機(jī)/監(jiān)控器 安裝類型:表面貼裝 封裝/外殼:28-WFQFN 裸露焊盤(pán) 供應(yīng)商設(shè)備封裝:28-WQFN(4x4)裸露焊盤(pán) 包裝:帶卷 (TR) 其它名稱:296-32523-2TPS65198RUYT-ND |

| X98027 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:PRELIMINARY INFORMATION |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。