- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376449 > X98014 (Intersil Corporation) 140MHz Triple Video Digitizer with Digital DLL(帶有數(shù)字PLL的140MHz三路視頻信號數(shù)字轉(zhuǎn)換器) PDF資料下載

參數(shù)資料

| 型號: | X98014 |

| 廠商: | Intersil Corporation |

| 英文描述: | 140MHz Triple Video Digitizer with Digital DLL(帶有數(shù)字PLL的140MHz三路視頻信號數(shù)字轉(zhuǎn)換器) |

| 中文描述: | 140MHz的三路視頻數(shù)字化與數(shù)字DLL(帶有數(shù)字鎖相環(huán)的140MHz的三路視頻信號數(shù)字轉(zhuǎn)換器) |

| 文件頁數(shù): | 25/29頁 |

| 文件大?。?/td> | 444K |

| 代理商: | X98014 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁

25

FN8217.3

March 8, 2006

This is a rarely used composite sync format; in most

applications it will never be encountered. However if this

CSYNC waveform must be supported, there is a simple

applications solution using an XOR gate.

The output of the XOR gate is connected to the HSYNC

IN

input of the X98014. One of the XOR inputs is connected to

the HSYNC/CSYNC source, and the other input is

connected to a general purpose I/O. For all sync sources

except the CSYNC shown in Figure 11, the input connected

to the GPIO should be driven low.

If the system microcontroller detects a mode corresponding

to the sync type and polarity shown in Figure 11, it should

drive the GPIO pin high. This will invert the CSYNC signal

seen by the X98014 and prevent any spontaneous image

shifting.

X98014 Serial Communication

Overview

The X98014 uses a 2 wire serial bus for communication with

its host. SCL is the Serial Clock line, driven by the host, and

SDA is the Serial Data line, which can be driven by all

devices on the bus. SDA is open drain to allow multiple

devices to share the same bus simultaneously.

Communication is accomplished in three steps:

1. The Host selects the X98014 it wishes to communicate

with.

2. The Host writes the initial X98014 Configuration Register

address it wishes to write to or read from.

3. The Host writes to or reads from the X98014’s

Configuration Register. The X98014’s internal address

pointer auto increments, so to read registers 0x00

through 0x1B, for example, one would write 0x00 in step

2, then repeat step 3 28 times, with each read returning

the next register value.

The X98014 has a 7 bit address on the serial bus. The upper

6 bits are permanently set to 100110, with the lower bit

determined by the state of pin 48. This allows 2 X98014s to

be independently controlled while sharing the same bus.

The bus is nominally inactive, with SDA and SCL high.

Communication begins when the host issues a START

command by taking SDA low while SCL is high (Figure 12).

The X98014 continuously monitors the SDA and SCL lines

for the start condition and will not respond to any command

until this condition has been met. The host then transmits the

7 bit serial address plus a R/W bit, indicating if the next

transaction will be a Read (R/W = 1) or a Write (R/W = 0). If

the address transmitted matches that of any device on the

bus, that device must respond with an ACKNOWLEDGE

(Figure 13).

Once the serial address has been transmitted and

acknowledged, one or more bytes of information can be

written to or read from the slave. Communication with the

selected device in the selected direction (read or write) is

ended by a STOP command, where SDA rises while SCL is

high (Figure 12), or a second START command, which is

commonly used to reverse data direction without

relinquishing the bus.

Data on the serial bus must be valid for the entire time SCL

is high (Figure 14). To achieve this, data being written to the

X98014 is latched on a delayed version of the rising edge of

SCL. SCL is delayed and deglitched inside the X98014 for 3

crystal clock periods (120ns for a 25MHz crystal) to eliminate

spurious clock pulses that could disrupt serial

communication.

When the contents of the X98014 are being read, the SDA

line is updated after the falling edge of SCL, delayed and

deglitched in the same manner.

Configuration Register Write

Figure 15 shows two views of the steps necessary to write

one or more words to the Configuration Register.

Configuration Register Read

Figure 16 shows two views of the steps necessary to read

one or more words from the Configuration Register.

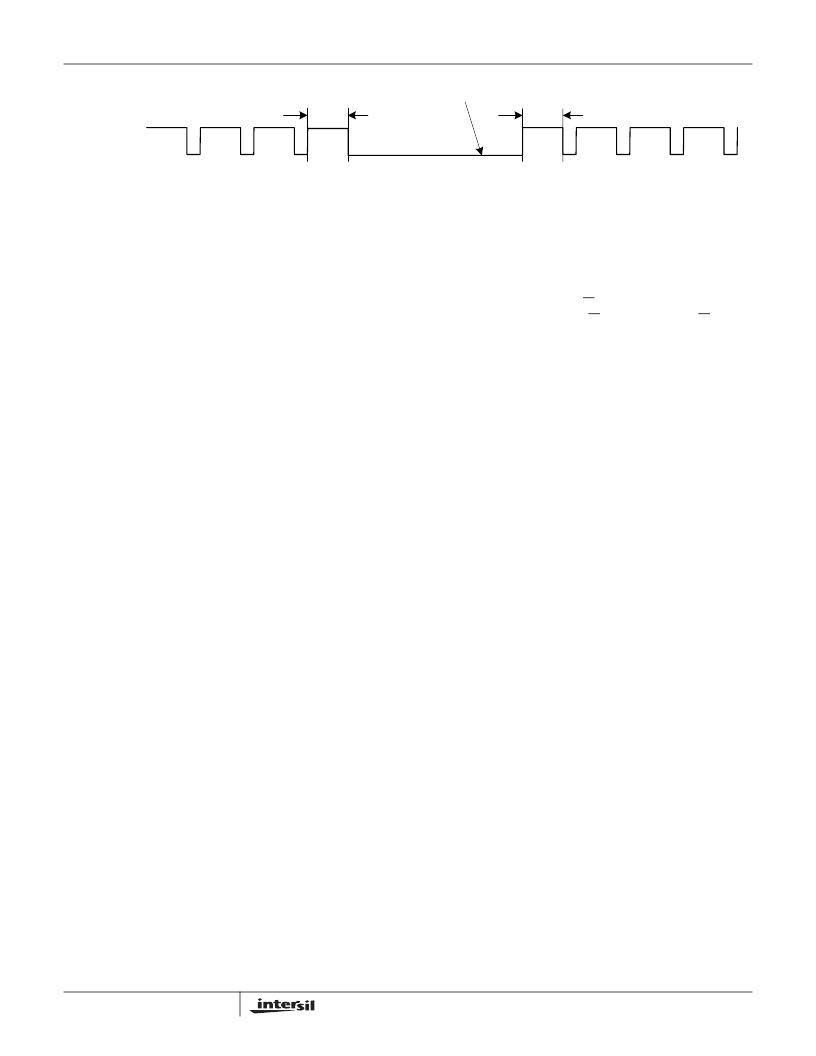

FIGURE 11. CSYNC ON HSYNC THAT MAY CAUSE SPORADIC IMAGE SHIFTS

t

1

t

2

HSYNC

IN

Conditions required: negative polarity VSYNC, with no serrations, and t

1

= t

2

X98014

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X98017 | 170MHz Triple Video Digitizer with Digital PLL |

| X98017L128-3.3 | GIGATRUE 550 CAT PATCH CABLE NO BOOT 20FT BLACK |

| X98017L128-3.3-Z | GIGATRUE 550 CAT PATCH CBL NO BOOT 20FT BK 25 PK |

| X98021 | 210MHz Triple Video Digitizer with Digital PLL |

| X98021L128-3.3 | 210MHz Triple Video Digitizer with Digital PLL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X98014_06 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:140MHz Triple Video Digitizer with Digital PLL |

| X98014L128-3.3 | 制造商:Intersil Corporation 功能描述:140MHz Triple Video Digitizer with Digital DLL |

| X98014L128-3.3-Z | 功能描述:IC VIDEO DIGITIZER TRPL 128MQFP RoHS:是 類別:集成電路 (IC) >> 線性 - 視頻處理 系列:- 標(biāo)準(zhǔn)包裝:250 系列:- 類型:電平移位器 應(yīng)用:LCD 電視機(jī)/監(jiān)控器 安裝類型:表面貼裝 封裝/外殼:28-WFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:28-WQFN(4x4)裸露焊盤 包裝:帶卷 (TR) 其它名稱:296-32523-2TPS65198RUYT-ND |

| X98017 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:170MHz Triple Video Digitizer with Digital PLL |

| X98017_06 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:170MHz Triple Video Digitizer with Digital PLL |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。