- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371281 > X9252YV24I-2.7 Quad Digitally-Controlled (XDCP) potentiometer PDF資料下載

參數(shù)資料

| 型號: | X9252YV24I-2.7 |

| 元件分類: | 數(shù)字電位計 |

| 英文描述: | Quad Digitally-Controlled (XDCP) potentiometer |

| 中文描述: | 四數(shù)字控制(數(shù)字電位器)電位 |

| 文件頁數(shù): | 16/21頁 |

| 文件大小: | 126K |

| 代理商: | X9252YV24I-2.7 |

X9252

16 of 21

REV 1.4.1 7/29/03

www.xicor.com

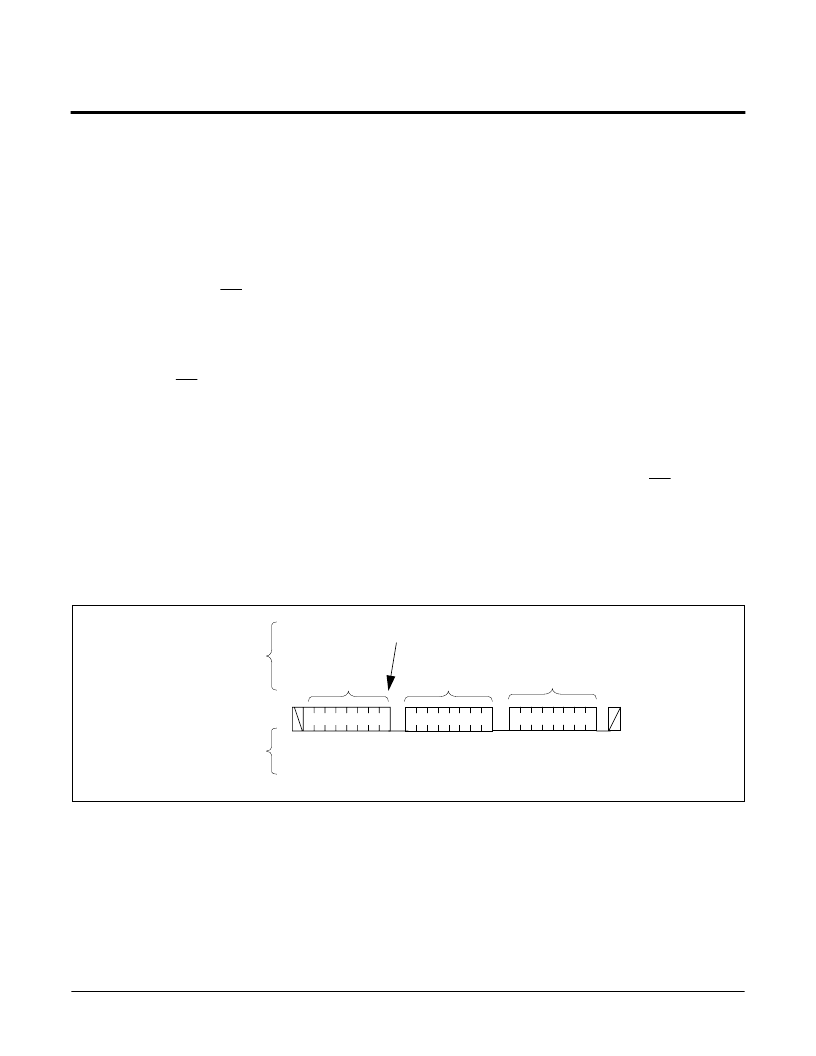

Byte Write Operation

For any Byte Write operation, the X9252 requires the

Slave Address byte, an Address Byte, and a Data Byte

(See Figure 6). After each of them, the X9252

responds with an ACK. The master then terminates the

transfer by generating a STOP condition. At this time, if

the write operation is to a volatile register (WCR, or

SR), the X9252 is ready for the next read or write

operation. If the write operation is to a nonvolatile

register (DR), and the WP pin is high, the X9252

begins the internal write cycle to the nonvolatile

memory. During the internal nonvolatile write cycle, the

X9252 does not respond to any requests from the

master. The SDA output is at high impedance.

The SR bits and WP pin determine the register being

accessed through the 2-wire interface. See Table 1 on

page 11.

As noted before, that any write operation to a Data

Register (DR), also writes to the WCR of the corre-

sponding DCP.

For example, to write 3Ahex to the Data Register 1 of

DCP2 the following sequence is required:

During the sequence of this example, WP pin must be

high, and A0, A1, and A2 pins must be low. When com-

pleted, the DR21 register will be set to 3Ah, and also

the WCR2.

Figure 6. Byte Write Sequence

START

Slave Address

ACK

Address Byte

ACK

Data Byte

ACK

STOP

0101 0000

0000 0111

0000 0011

START

Slave Address

ACK

Address Byte

ACK

Data Byte

ACK

STOP

0101 0000

0000 0010

0011 1010

(Hardware Address = 000,

and a Write command)

(Indicates Status Register

address)

(Data Register 1 and

NVEnable selected)

(Hardware address = 000,

Write command)

(Access DCP2)

(Write Data Byte 3Ah)

S

t

a

r

t

S

t

o

p

Slave

Address

Address

Byte

Data

Byte

A

C

K

Signals from

the Master

Signals from

the Slave

A

C

K

0

0

0

1

1

A

C

K

Write

Signal at SDA

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X9252TV24I-2.7 | Quad Digitally-Controlled (XDCP) potentiometer |

| X9252UV24-2.7 | Quad Digitally-Controlled (XDCP) potentiometer |

| X9252TV24-2.7 | Quad Digitally-Controlled (XDCP) potentiometer |

| X9252 | Quad Digitally-Controlled (XDCP) potentiometer |

| X9252WV24-2.7 | Quad Digitally-Controlled (XDCP) potentiometer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X9252YV24IZ-2.7 | 功能描述:IC POT DGTL QUAD 24-TSSOP RoHS:是 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 數(shù)字電位器 系列:XDCP™ 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 接片:256 電阻(歐姆):100k 電路數(shù):1 溫度系數(shù):標準值 35 ppm/°C 存儲器類型:非易失 接口:3 線串口 電源電壓:2.7 V ~ 5.25 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:8-WDFN 裸露焊盤 供應(yīng)商設(shè)備封裝:8-TDFN-EP(3x3) 包裝:剪切帶 (CT) 產(chǎn)品目錄頁面:1399 (CN2011-ZH PDF) 其它名稱:MAX5423ETA+TCT |

| X9258 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Low Noise/Low Power/2-Wire Bus/256 Taps |

| X9258)06 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Quad Digital Controlled Potentiometers |

| X9258_11 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Quad Digital Controlled Potentiometers(XDCP?) |

| X9258_13 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Low Noise/Low Power/2-Wire Bus/256 Taps |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。