- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371201 > X24640S8I 400KHz 2-Wire Serial E 2 PROM with Block Lock PDF資料下載

參數(shù)資料

| 型號: | X24640S8I |

| 英文描述: | 400KHz 2-Wire Serial E 2 PROM with Block Lock |

| 中文描述: | 400kHz的2線串行E的2座鎖胎膜早破 |

| 文件頁數(shù): | 10/17頁 |

| 文件大?。?/td> | 85K |

| 代理商: | X24640S8I |

X24640

10

reset, nor can RWEL and WEL be reset in one write

operation. RWEL can be reset by writing 00000010 to

FFFFh; but this is the same operation as in step 3

described below, and will result in programing BL0,

BL1, and WPEN.

Writing to the BL and WPEN Bits

A 3 step sequence is required to change the nonvola-

tile Block Lock Protect or Write Protect Enable bits:

1)

Set WEL=1, Write 00000010 to address FFFFh

(Volatile Write Cycle.)

2)

Set RWEL=1, Write 00000110 to address FFFFh

(Volatile Write Cycle.)

3)

Set BL1, BL0, and/or WPEN bits, Write u00xy010 to

address FFFFh, where u=WPEN, x=BL1, and y=BL0.

(Nonvolatile Write Cycle.)

The three step sequence was created to make it diffi-

cult to change the contents of the Write Protect

Register accidentally. If WEL was set to one by a

previous register write operation, the user may start at

step 2. RWEL is reset to zero in step 3 so that user is

required to perform steps 2 and 3 to make another

change. RWEL must be 0 in step 3. If the RWEL bit in

the data byte for step 3 is a one, then no changes are

made to the Write Protect Register and the device

remains at step 2.

The WP pin must be LOW or the WPEN bit must be

LOW before a nonvolatile register write operation is

initiated. Otherwise, the write operation will abort and

the device will go into standby mode after the master

issues the stop condition in step 3.

Step 3 is a nonvolatile write operation, requiring t

WC

to

complete (acknowledge polling may be used to reduce

this time requirement). It should be noted that step 3

MUST end with a stop condition. If a start condition is

issued during or at the end of step 3 (instead of a stop

condition) the device will abort the nonvolatile register

write and remain at step 2. If the operation is aborted

with a start condition, the master must issue a stop to

put the device into standby mode.

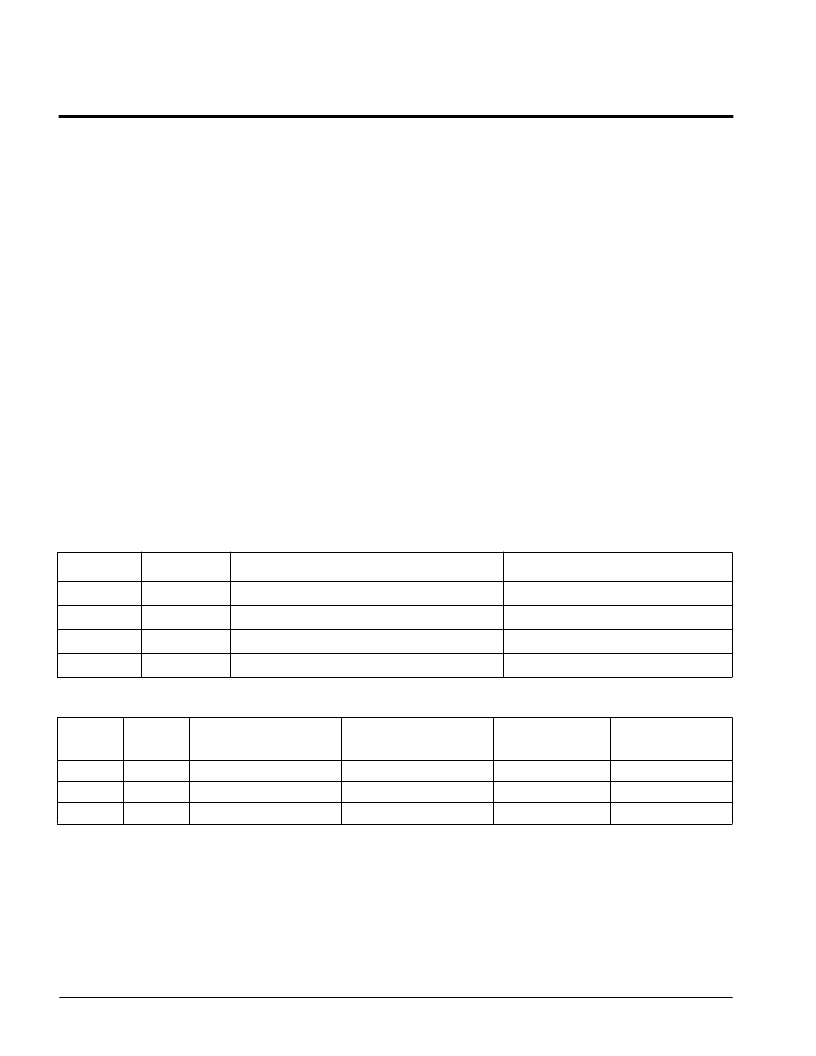

Figure 11. Block Lock Protect Bits and Protected Addresses

7038 FRM T02

Figure 12. WP Pin and WPEN Bit Functionality

7038 FRM T03

BL1

BL0

Protected Addresses

Array Location

0

0

None

No Protect

0

1

1800h - 1FFFh

Upper 1/4

1

0

1000h - 1FFFh

Upper 1/2

1

1

0000h - 1FFFh

Full Array

WP

WPEN

Memory Array Not

Lock Block Protected

Memory Array Block

Lock Protected

Block Lock Bits

WPEN

Bit

0

X

1

X

0

1

Writable

Writable

Writable

Protected

Protected

Protected

Unprotected

Unprotected

Protected

Unprotected

Unprotected

Protected

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X24640V20-2.5 | 400KHz 2-Wire Serial E 2 PROM with Block Lock |

| X24640V20I-2.5 | 400KHz 2-Wire Serial E 2 PROM with Block Lock |

| X24640S8I-2.5 | 400KHz 2-Wire Serial E 2 PROM with Block Lock |

| X24640P-2.5 | 400KHz 2-Wire Serial E 2 PROM with Block Lock |

| X24641S8I-1.8 | 400 KHz 2-Wire Serial E 2 PROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X24640S8I-1.8 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:400KHz 2-Wire Serial E 2 PROM with Block Lock |

| X24640S8I-2.5 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:400KHz 2-Wire Serial E 2 PROM with Block Lock |

| X24640V20 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:400KHz 2-Wire Serial E 2 PROM with Block Lock |

| X24640V20-1.8 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:400KHz 2-Wire Serial E 2 PROM with Block Lock |

| X24640V20-2.5 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:400KHz 2-Wire Serial E 2 PROM with Block Lock |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。