- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄140370 > WEDPZ512K72V-100BC (WHITE ELECTRONIC DESIGNS CORP) 512K X 72 ZBT SRAM, 5 ns, PBGA152 PDF資料下載

參數(shù)資料

| 型號(hào): | WEDPZ512K72V-100BC |

| 廠商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分類: | SRAM |

| 英文描述: | 512K X 72 ZBT SRAM, 5 ns, PBGA152 |

| 封裝: | 17 X 23 MM, PLASTIC, BGA-152 |

| 文件頁(yè)數(shù): | 9/15頁(yè) |

| 文件大小: | 0K |

| 代理商: | WEDPZ512K72V-100BC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)

3

White Electronic Designs Corporation (602) 437-1520 www.wedc.com

White Electronic Designs

WEDPZ512K72V-XBX

February 2009

Rev. 9

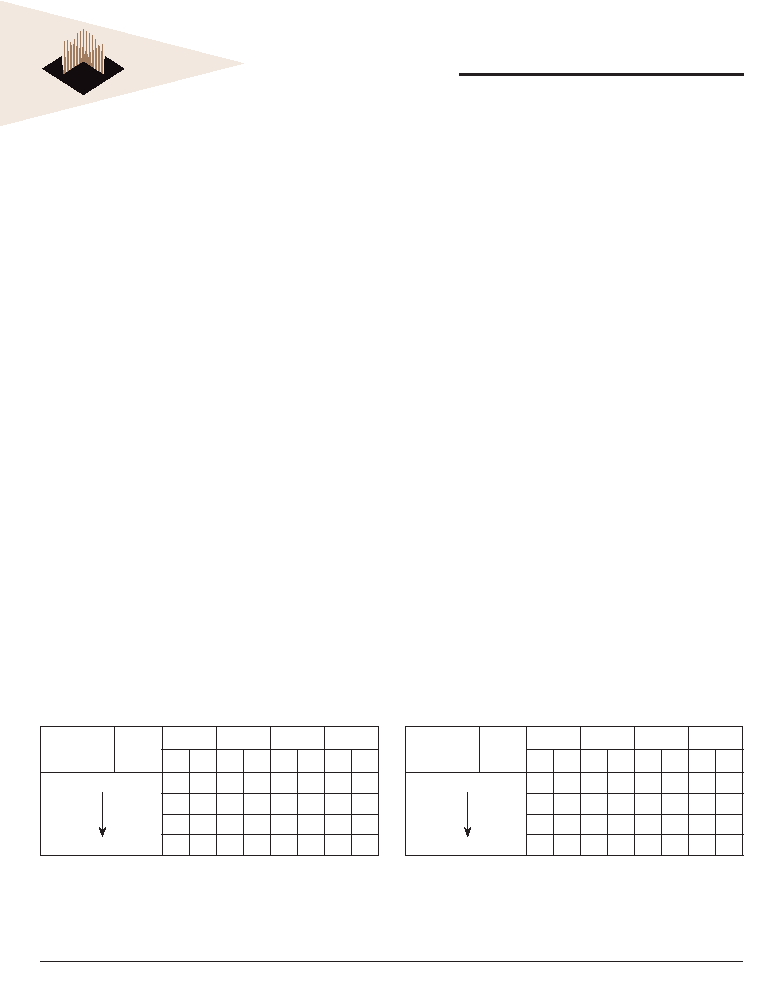

BURST SEQUENCE TABLE

Write operation occurs when WE# is driven low at the

rising edge of the clock. BW#[h:a] can be used for byte

write operation. The pipe-lined ZBL SSRAM uses a late-

late write cycle to utilize 100% of the bandwidth. At the rst

rising edge of the clock, WE# and address are registered,

and the data associated with that address is required two

cycles later.

Subsequent addresses are generated by ADV High for

the burst access as shown below. The starting point of the

burst sequence is provided by the external address. The

burst address counter wraps around to its initial state upon

completion. The burst sequence is determined by the state

of the LBO# pin. When this pin is low, linear burst sequence

is selected. And when this pin is high, Interleaved burst

sequence is selected.

During normal operation, ZZ must be driven low. When ZZ

is driven high, the SRAM will enter a Power Sleep Mode

after two cycles. At this time, internal state of the SRAM

is preserved. When ZZ returns to low, the SRAM operates

after two cycles of wake up time.

(Interleaved Burst, LBO# = High)

LBO# Pin

High

Case 1

Case 2

Case 3

Case 4

A1

A0

A1

A0

A1

A0

A1

A0

First Address

Fourth Address

00011011

01001110

10110001

11100100

NOTE 1: LBO pin must be tied to High or Low, and Floating State must not be allowed.

(Linear Burst, LBO# = Low)

LBO# Pin

High

Case 1

Case 2

Case 3

Case 4

A1

A0

A1

A0

A1

A0

A1

A0

First Address

Fourth Address

00011011

01101100

10110001

11000110

FUNCTION DESCRIPTION

The WEDPZ512K72V-XBX is an ZBL SSRAM designed

to sustain 100% bus bandwidth by eliminating turnaround

cycle when there is transition from Read to Write, or vice

versa. All inputs (with the exception of OE#, LBO# and ZZ)

are synchronized to rising clock edges.

All read, write and deselect cycles are initiated by the

ADV input. Subsequent burst addresses can be internally

generated by the burst advance pin (ADV). ADV should

be driven to Low once the device has been deselected in

order to load a new address for next operation.

Clock Enable (CKE#) pin allows the operation of the chip to

be suspended as long as necessary. When CKE# is high,

all synchronous inputs are ignored and the internal device

registers will hold their previous values. NBL SSRAM

latches external address and initiates a cycle when CKE

and ADV are driven low at the rising edge of the clock.

Output Enable (OE#) can be used to disable the output at

any given time. Read operation is initiated when at the rising

edge of the clock, the address presented to the address

inputs are latched in the address register, CKE# is driven

low, the write enable input signals WE# are driven high,

and ADV driven low. The internal array is read between

the rst rising edge and the second rising edge of the clock

and the data is latched in the output register. At the second

clock edge the data is driven out of the SRAM. During read

operation OE# must be driven low for the device to drive

out the requested data.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| WS128K32-20G1UC | 128K X 32 MULTI DEVICE SRAM MODULE, 20 ns, CQFP68 |

| WS128K32-25G1TCA | 128K X 32 MULTI DEVICE SRAM MODULE, 25 ns, CQFP68 |

| WS128K32-25G1TQA | 128K X 32 MULTI DEVICE SRAM MODULE, 25 ns, CQFP68 |

| WS128K32-35G1UM | 128K X 32 MULTI DEVICE SRAM MODULE, 35 ns, CQFP68 |

| WS128K32-55G1TMA | 128K X 32 MULTI DEVICE SRAM MODULE, 55 ns, CQFP68 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| WEDPZ512K72V-100BI | 制造商:Microsemi Corporation 功能描述:512K X 72 ZBL SSRAM MODULE, 3.3V, 100MHZ, 152 BGA 17MM X 23M - Bulk |

| WEDPZ512K72V-100BM | 制造商:Microsemi Corporation 功能描述:512K X 72 ZBL SSRAM MODULE, 3.3V, 100MHZ, 152 BGA 17MM X 23M - Bulk |

| WEDPZ512K72V-133BC | 制造商:Microsemi Corporation 功能描述:512K X 72 ZBL SSRAM MODULE, 3.3V, 133MHZ, 152 BGA 17MM X 23M - Bulk |

| WEDPZ512K72V-133BI | 制造商:Microsemi Corporation 功能描述:512K X 72 ZBL SSRAM MODULE, 3.3V, 133MHZ, 152 BGA 17MM X 23M - Bulk |

| WEDPZ512K72V-133BM | 制造商:Microsemi Corporation 功能描述:512K X 72 ZBL SSRAM MODULE, 3.3V, 133MHZ, 152 BGA 17MM X 23M - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。