- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄68457 > W3H64M72E-SBC (MICROSEMI CORP-PMG MICROELECTRONICS) 64M X 72 DDR DRAM, PBGA208 PDF資料下載

參數(shù)資料

| 型號: | W3H64M72E-SBC |

| 廠商: | MICROSEMI CORP-PMG MICROELECTRONICS |

| 元件分類: | DRAM |

| 英文描述: | 64M X 72 DDR DRAM, PBGA208 |

| 封裝: | 17 X 23 MM, 1 MM PITCH, PLASTIC, BGA-208 |

| 文件頁數(shù): | 20/30頁 |

| 文件大?。?/td> | 999K |

| 代理商: | W3H64M72E-SBC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁

W3H64M72E-XSBX

27

White Electronic Designs Corporation (602) 437-1520 www.wedc.com

White Electronic Designs

December 2006

Rev. 2

ADVANCED*

White Electronic Designs Corp. reserves the right to change products or specications without notice.

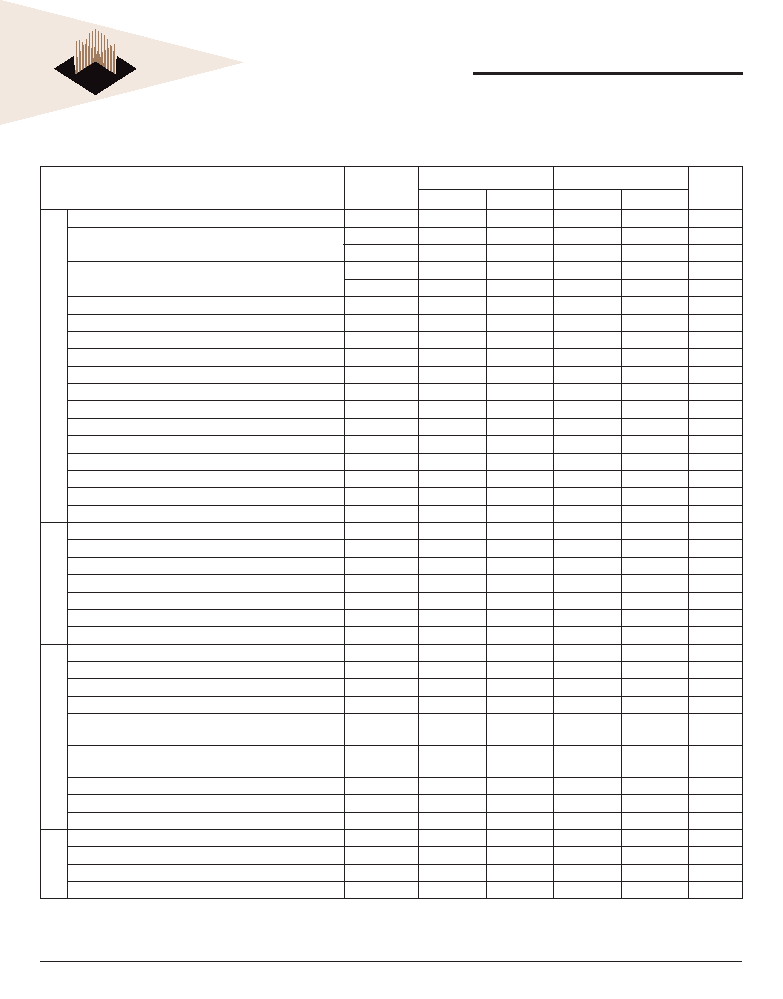

AC TIMING PARAMETERS

(continued)

-55°C ≤ TA < +125°C; VCCQ = + 1.8V ± 0.1V, VCC = +1.8V ± 0.1V

Parameter

Symbol

533Mbs CL4

400Mbs CL3

Unit

Min

Max

Min

Max

Command

and

Address

Address and control input pulse width for each input

t

IPW

0.6

tCK

Address and control input setup time

t

ISa

500

600

ps

t

ISb

250

350

ps

Address and control input hold time

t

IHa

500

600

ps

t

IHb

375

475

ps

CAS# to CAS# command delay

t

CCD

2

ps

ACTIVE to ACTIVE (same bank) command

t

RC

55

ns

ACTIVE bank a to ACTIVE bank b command

t

RRD

10

ns

ACTIVE to READ or WRITE delay

t

RCD

15

ns

Four Bank Activate period

t

FAW

50

ns

ACTIVE to PRECHARGE command

t

RAS

40

70,000

40

70,000

ns

Internal READ to precharge command delay

t

RTP

7.5

ns

Write recovery time

t

WR

15

ns

Auto precharge write recovery + precharge time

t

DAL

tWR + tRP

ns

Internal WRITE to READ command delay

t

WTR

7.5

10

ns

PRECHARGE command period

t

RP

15

ns

PRECHARGE ALL command period

t

RPA

tRP + tCK

ns

LOAD MODE command cycle time

t

MRD

2

tCK

Self

Refresh

CKE low to CK, CK# uncertainty

t

DELAY

tIS +tIH + tCK

ns

REFRESH to Active or Refresh to Refresh command interval

t

RFC

127.5

70,000

127.5

70,000

ns

Average periodic refresh interval (commercial)

t

REFI

7.8

s

Average periodic refresh interval (industrial)

t

REFIIT

3.9

s

Exit self refresh to non-READ command

t

XSNR

tRPC(MIN) + 10

tRFC(MIN) + 10

ns

Exit self refresh to READ

t

XSRD

200

tCK

Exit self refresh timing reference

t

lSXR

tIS

ps

ODT

ODT tum-on delay

t

AOND

2222

tCK

ODT turn-on

t

ACN

tAC(MIN)

tAC(MAX) + 1000

tAC(MIN)

tAC(MAX) + 1000

ps

ODT turn-off delay

t

AOFD

2.5

tCK

ODT tum-off

tAOF

tAC(MIN)

tAC(MAX) + 600

tAC(MIN)

tAC(MAX) + 600

ps

ODT tum-on (power-down mode)

t

AONPD

tAC(MIN) +

2000

2 x tCK +

tAC(MAX) + 1000

tAC(MIN) +

2000

2 x tCK +

tAC(MAX) + 1000

ps

ODT turn-off (power-down mode)

t

AOFPD

tAC(MIN) +

2000

2 x tCK +

tAC(MAX) + 1000

tAC(MIN) +

2000

2 x tCK +

tAC(MAX) + 1000

ps

ODT to power-down entry latency

t

ANPD

3

tCK

ODT power-down exit latency

t

AXPD

8

tCK

ODT enable from MRS command

t

MOD

12

ns

Power-Down

Exit active power-down to READ command, MR[bit12=0]

t

XARD

2

tCK

Exit active power-down to READ command, MR[bit12=1]

t

XARDS

6-AL

tCK

Exit precharge power-down to any non-READ command

t

XP

2

tCK

CKE minimum high/low time

t

CKE

3

tCK

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W3H64M72E-400ESC | 64M X 72 DDR DRAM, 0.6 ns, PBGA208 |

| W3H64M72E-667ES | 64M X 72 DDR DRAM, PBGA208 |

| W3HG128M64EEU534D4IMG | 128M X 64 DDR DRAM MODULE, 0.5 ns, ZMA200 |

| W3HG128M64EEU806D4SG | 128M X 64 DDR DRAM MODULE, 0.45 ns, ZMA200 |

| W3HG128M64EEU665D4ISG | 128M X 64 DDR DRAM MODULE, 0.45 ns, ZMA200 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W3H64M72E-SBI | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:64M x 72 DDR2 SDRAM 208 PBGA Multi-Chip Package |

| W3H64M72E-SBM | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:64M x 72 DDR2 SDRAM 208 PBGA Multi-Chip Package |

| W3H64M72E-XSBX | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:64M x 72 DDR2 SDRAM 208 PBGA Multi-Chip Package |

| W3HG128M64EEU403D4XXG | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:1GB - 128Mx64 DDR2 SDRAM UNBUFFERED, SO-DIMM |

| W3HG128M64EEU534D4XXG | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:1GB - 128Mx64 DDR2 SDRAM UNBUFFERED, SO-DIMM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。