- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄245685 > W3H128M72ER-667SBC (WHITE ELECTRONIC DESIGNS CORP) 128M X 72 DDR DRAM, 0.5 ns, PBGA255 PDF資料下載

參數(shù)資料

| 型號: | W3H128M72ER-667SBC |

| 廠商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分類: | DRAM |

| 英文描述: | 128M X 72 DDR DRAM, 0.5 ns, PBGA255 |

| 封裝: | 23 X 21 MM, 1.27 MM PITCH, PLASTIC, BGA-255 |

| 文件頁數(shù): | 29/34頁 |

| 文件大小: | 1028K |

| 代理商: | W3H128M72ER-667SBC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁

W3H128M72ER-XNBX

4

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

February 2009

Rev. 6

PRELIMINARY

White Electronic Designs Corp. reserves the right to change products or specications without notice.

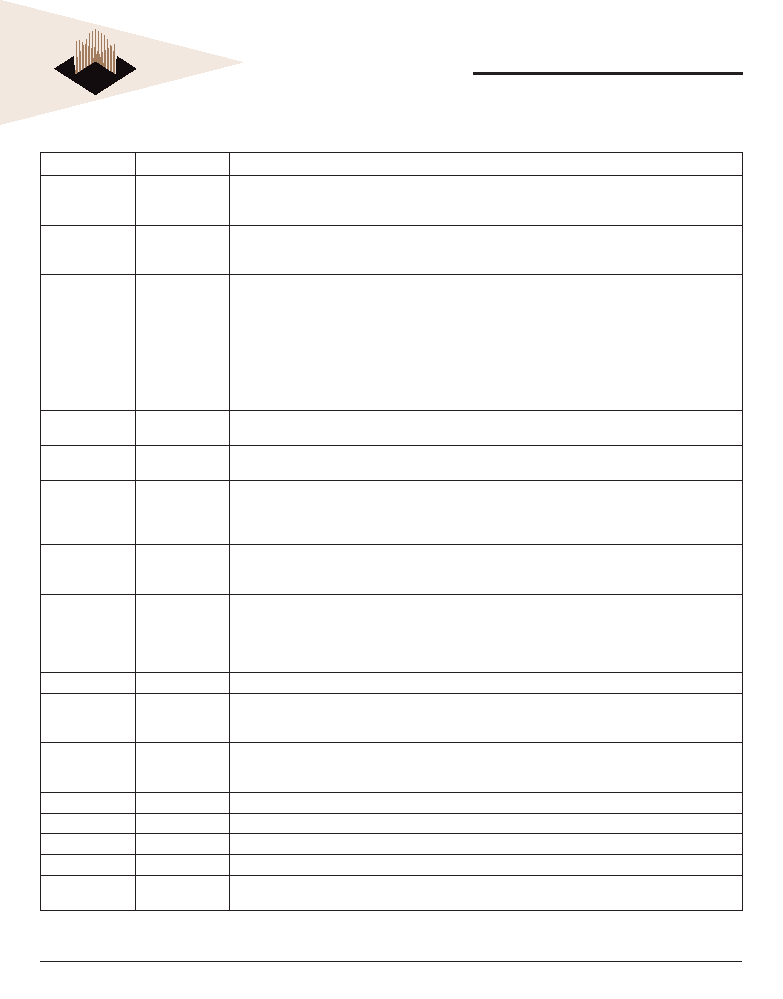

TABLE 1 – BALL DESCRIPTIONS

Symbol

Type

Description

ODT

Input

On-Die termination: ODT (registered HIGH) enables termination resistance internal to the DDR2 SDRAM. When

enabled, ODT is only applied to each of the following balls: DQ0–DQ71, LDM, UDM, LDQS, LDQS#, UDQS, and

UDQS#. The ODT input will be ignored if disabled via the LOAD MODE command.

CK, CK#

Input

Clock: CK and CK# are differential clock inputs. All address and control input signals are sampled on the crossing

of the positive edge of CK and negative edge of CK#. Output data (DQs and DQS/DQS#) is referenced to the

crossings of CK and CK#.

CKE

Input

Clock enable: CKE (registered HIGH) activates and CKE (registered LOW) deactivates clocking circuitry on the

DDR2 SDRAM. The specic circuitry that is enabled/disabled is dependent on the DDR2 SDRAM conguration

and operating mode. CKE LOW provides PRECHARGE power-down mode and SELF-REFRESH action (all banks

idle), or ACTIVE power-down (row active in any bank). CKE is synchronous for power-down entry, Power-down

exit, output disable, and for self refresh entry. CKE is asynchronous for self refresh exit. Input buffers (excluding

CKE, and ODT) are disabled during power-down. Input buffers (excluding CKE) are disabled during self refresh.

CKE is an SSTL_18 input but will detect a LVCMO SLOW level once VCC is applied during rst power-up. After

VREF has become stable during the power on and initialization sequence, it must be maintained for proper

operation of the CKE receiver. For proper SELF-REFRESH operation, VREF must be maintained.

CS#

Input

Chip select: CS# enables (registered LOW) and disables (registered HIGH) the command decoder. All commands

are masked when CS# is registered HIGH.

RAS#, CAS#,

WE#

Input

Command inputs: RAS#, CAS#, WE# (along with CS#) dene the command being entered.

LDM, UDM

Input

Input data mask: DM is an input mask signal for write data. Input data is masked when DM is concurrently sampled

HIGH during a WRITE access. DM is sampled on both edges of DQS. Although DM balls are input-only, the DM

loading is designed to match that of DQ and DQS balls. LDM is DM for lower byte DQ0–DQ7 and UDM is DM for

upper byte DQ8–DQ15, of each of U0-U4

BA0–BA2

Input

Bank address inputs: BA0–BA2 dene to which bank an ACTIVE, READ, WRITE, or PRECHARGE command is

being applied. BA0–BA2 dene which mode register including MR, EMR, EMR(2), and EMR(3) is loaded during the

LOAD MODE command.

A0-A13

Input

Address inputs: Provide the row address for ACTIVE commands, and the column address and auto precharge bit

(A10) for READ/WRITE commands, to select one location out of the memory array in the respective bank. A10

sampled during a PRECHARGE command determines whether the PRECHARGE applies to one bank (A10 LOW,

bank selected by BA2–BA0) or all banks (A10 HIGH) The address inputs also provide the op-code during a LOAD

MODE command.

DQ0-63

I/O

Data input/output: Bidirectional data bus

UDQS, UDQS#

I/O

Data strobe for upper byte: Output with read data, input with write data for source synchronous operation. Edge-

aligned with read data, center-aligned with write data. UDQS# is only used when differential data strobe mode is

enabled via the LOAD MODE command.

LDQS, LDQS#

I/O

Data strobe for lower byte: Output with read data, input with write data for source synchronous operation. Edge-

aligned with read data, center-aligned with write data. LDQS# is only used when differential data strobe mode is

enabled via the LOAD MODE command.

VCC

Supply

Power Supply: I/O + Core; VCCQ is common to VCC

VREF

Supply

SSTL_18 reference voltage.

VSS

Supply

Ground

NC

-

No connect: These balls should be left unconnected.

DNU

-

Future use; address bits A14 and A15 are reserved for future densities. Address bits F1, F2, and G2 are reserved

for optional parity function

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W3H128M72ER-667SBM | 128M X 72 DDR DRAM, 0.5 ns, PBGA255 |

| W3EG72126S262AJD3SG | 128M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

| W3EG72126S265JD3SG | 128M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

| W3H128M72E0533SBM | DDR DRAM, PBGA208 |

| W3H128M72E2-533NBC | 128M X 72 DDR DRAM, 0.5 ns, PBGA208 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W3H13C1048AT | 制造商:AVX 制造商全稱:AVX Corporation 功能描述:High Current Feedthry Capacitors |

| W3H13C1048AT1A | 功能描述:饋通電容器 25volt 0.1uF X7R RoHS:否 制造商:Tusonix 電容:8200 pF 容差:- 20 %, + 80 % 電壓額定值: 工作溫度范圍: 溫度系數(shù): 封裝 / 箱體: |

| W3H13C1048AT1F | 功能描述:饋通電容器 25volt 0.1uF X7R RoHS:否 制造商:Tusonix 電容:8200 pF 容差:- 20 %, + 80 % 電壓額定值: 工作溫度范圍: 溫度系數(shù): 封裝 / 箱體: |

| W3H15C1038AT | 制造商:AVX 制造商全稱:AVX Corporation 功能描述:High Current Feedthry Capacitors |

| W3H15C1038AT1A | 功能描述:饋通電容器 50volt .01uF X7R RoHS:否 制造商:Tusonix 電容:8200 pF 容差:- 20 %, + 80 % 電壓額定值: 工作溫度范圍: 溫度系數(shù): 封裝 / 箱體: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。