- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361728 > VES1993 (NXP SEMICONDUCTORS) Single Chip Satellite Channel Receiver(單片衛(wèi)星頻道接收器) PDF資料下載

參數(shù)資料

| 型號: | VES1993 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | Single Chip Satellite Channel Receiver(單片衛(wèi)星頻道接收器) |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封裝: | MQFP-100 |

| 文件頁數(shù): | 9/16頁 |

| 文件大小: | 90K |

| 代理商: | VES1993 |

1999 Jan 01

9

Philips Semiconductors

Product specification

Single Chip Satellite Channel Receiver

VES1993

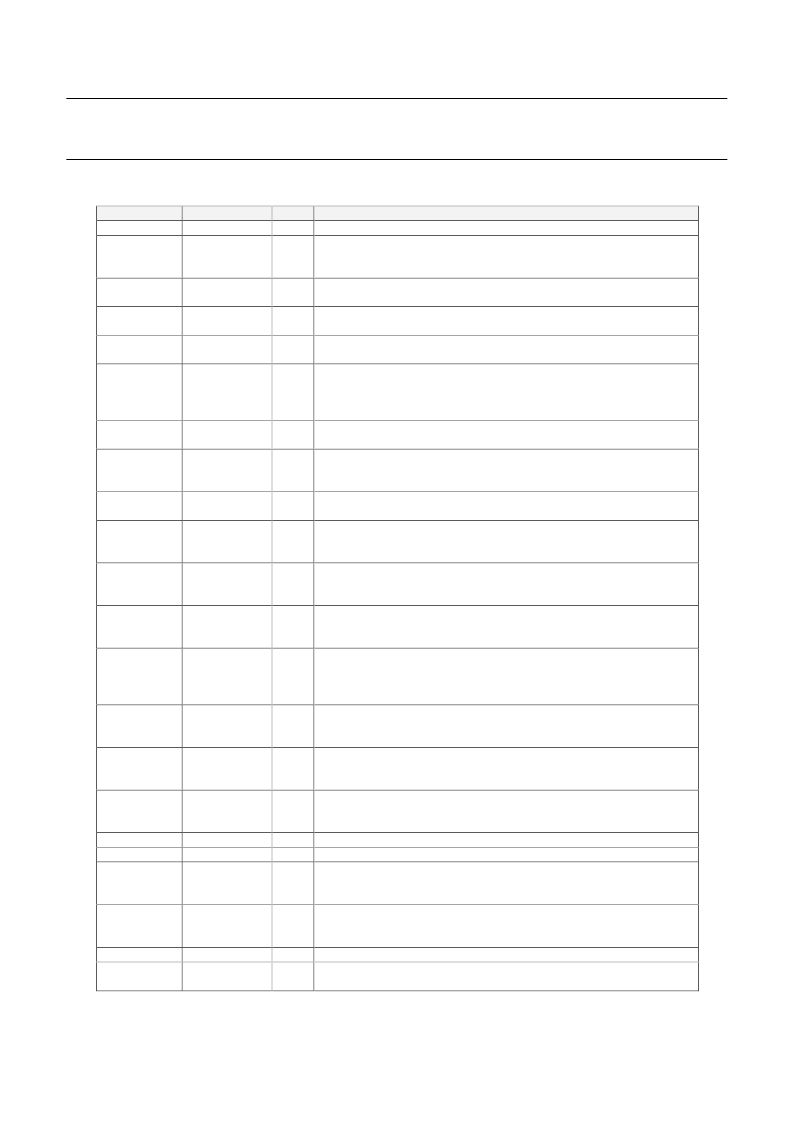

Symbol

Pin Number

Type

Description

Reference source not found.

,

Error! Reference source not found.

)

Output CLock. OCLK is the output clock for the parallel DO[7:0] outputs.

OCLK is internally generated depending on which type of interface is

selected.

Data ENable : this output signal is high when there is valid data on bus

DO[7:0].

UNCORrectable packet. This output signal goes high on a rising edge of

OCLK when the provided packet is uncorrectable.

Pulse SYNChro. This output signal goes high on a rising edge of OCLK

each time the first byte of a packet is provided.

Front End Locked. This output signal goes high when the demodulator,

the Viterbi decoder and the de-interleaver are all synchronized. FEL is

an open drain output and therefore requires an external pull up resistor

to either VDD or VCC.

TEST input. This input pin must be grounded for normal operation of the

VES 1993.

Test ReSeT. This active low input signal is used to reset the TAP

controller when in boundary scan mode. In normal mode of operation

TRST must be set low.

Test Data Out. This is the serial Test output pin used in boundary scan

mode. Serial Data are provided on the falling edge of TCK.

Test ClocK : an independant clock used to drive the TAP controller when

in boundary scan mode. In normal mode of operation, TCK must be

grounded.

Test Data In. The serial input for Test data and instruction when in

boundary scan mode. In normal mode of operation, TDI must be set to

GND or VDD.

Test Mode Select. This input signal provides the logic levels needed to

change the TAP controller from state to state. In normal mode of

operation, TMS must be set to VDD.

SADDR[2:0] input signals are the 3 LSBs of the I2C address of the VES

1993.The MSBs are internally set to 0001. Therefore the complete I2C

address of the VES 1993 is (MSB to LSB) : 0, 0, 0, 1, SADDR[2],

SADDR[1], SADDR[0].

SDA is a bidirectional signal. It is the serial input/output of the I2C

internal block. A pull-up resistor (typically 2.2 k) must be connected

between SDA and VCC for proper operation (Open Drain output).

I2C clock input. SCL should nominally be a square wave with a

maximum frequency of 400 KHz. SCL is generated by the system I2C

master.

These pins allow to select the frequency of the I2C system clock,

depending on the crystal frequency. Internal I2C clock is a division of

XIN by 2

Analog signal Input for channel I.

Analog signal Input for channel Q.

Analog negative voltage reference. A decoupling capacitor of typically

0.1mF must be placed as closed as possible between VREFP and

VREFN. The typical voltage value at VREFN is 1.25V.

Analog positive voltage reference. A decoupling capacitor of typically 0.1

μ

F must be placed as closed as possible between VREFP and VREFN.

The typical voltage value at VREFP is 2V.

Analog positive supply voltage. AVD is typically 3.3V.

Analog ground voltage. A 0.1

μ

F decoupling capacitor must be placed

between AVD and AVS.

OCLK

72

O

3.3V

DEN

73

O

3.3V

O

3.3V

O

3.3V

O

5V

UNCOR

74

PSYNC

76

FEL

80

TEST

84

I

TRST

85

I

TDO

86

O

5V

I

TCK

88

TDI

89

I

TMS

90

I

SADDR[2:0]

31,32,33

I

SDA

36

I/O

5V

SCL

37

I

IICDIV[1:0]

12,15

I

IICDIV

(IICDIV from 1 to 3) and must be between 6 and 20 MHz.

VIN1

VIN2

VREFN

41

45

42

I

I

O

VREFP

46

O

AVD

AVS

43

44

I

I

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VES9600 | Single Chip DVB-T Channel Receiver(單片DVB-T頻道接收器) |

| VESTIGIALSAWS | Vestigial Sideband Filters for Professional Applications |

| VF150CSM | Peripheral IC |

| VF150T | Peripheral IC |

| VF150T1 | Peripheral IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VES-220M0JTR-0405 | 功能描述:鋁質(zhì)電解電容器-SMD 6.3 Volts 22uF 20% 4x5.3 RoHS:否 制造商:Vishay/BC Components 電容:2200 uF 容差:20 % 電壓額定值:16 V ESR: 工作溫度范圍:- 55 C to + 150 C 尺寸:16 mm W x 16 mm L x 21 mm H 產(chǎn)品:High Temp Electrolytic Capacitors |

| VES-220M1ATR-0505 | 功能描述:鋁質(zhì)電解電容器-SMD 10 Volts 22uF 20% 5x5.3 RoHS:否 制造商:Vishay/BC Components 電容:2200 uF 容差:20 % 電壓額定值:16 V ESR: 工作溫度范圍:- 55 C to + 150 C 尺寸:16 mm W x 16 mm L x 21 mm H 產(chǎn)品:High Temp Electrolytic Capacitors |

| VES-220M1CTR-0505 | 功能描述:鋁質(zhì)電解電容器-SMD 16 Volts 22uF 20% 5x5.3 RoHS:否 制造商:Vishay/BC Components 電容:2200 uF 容差:20 % 電壓額定值:16 V ESR: 工作溫度范圍:- 55 C to + 150 C 尺寸:16 mm W x 16 mm L x 21 mm H 產(chǎn)品:High Temp Electrolytic Capacitors |

| VES-220M1ETR-0605 | 功能描述:鋁質(zhì)電解電容器-SMD 25 Volts 22uF 20% 6.3x5.3 RoHS:否 制造商:Vishay/BC Components 電容:2200 uF 容差:20 % 電壓額定值:16 V ESR: 工作溫度范圍:- 55 C to + 150 C 尺寸:16 mm W x 16 mm L x 21 mm H 產(chǎn)品:High Temp Electrolytic Capacitors |

| VES-220M1HTR-0605 | 功能描述:鋁質(zhì)電解電容器-SMD 50 Volts 22uF 20% 6.3x5.3 RoHS:否 制造商:Vishay/BC Components 電容:2200 uF 容差:20 % 電壓額定值:16 V ESR: 工作溫度范圍:- 55 C to + 150 C 尺寸:16 mm W x 16 mm L x 21 mm H 產(chǎn)品:High Temp Electrolytic Capacitors |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。