- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄202172 > V59C1G01168QBLJ-25I (PROMOS TECHNOLOGIES INC) DDR DRAM, PBGA84 PDF資料下載

參數(shù)資料

| 型號(hào): | V59C1G01168QBLJ-25I |

| 廠商: | PROMOS TECHNOLOGIES INC |

| 元件分類: | DRAM |

| 英文描述: | DDR DRAM, PBGA84 |

| 封裝: | GREEN, FBGA-84 |

| 文件頁(yè)數(shù): | 71/82頁(yè) |

| 文件大?。?/td> | 995K |

| 代理商: | V59C1G01168QBLJ-25I |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)當(dāng)前第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)

73

ProMOS TECHNOLOGIES

V59C1G01(408/808/168)QB

V59C1G01(408/808/168)QB Rev. 1.1 December 2008

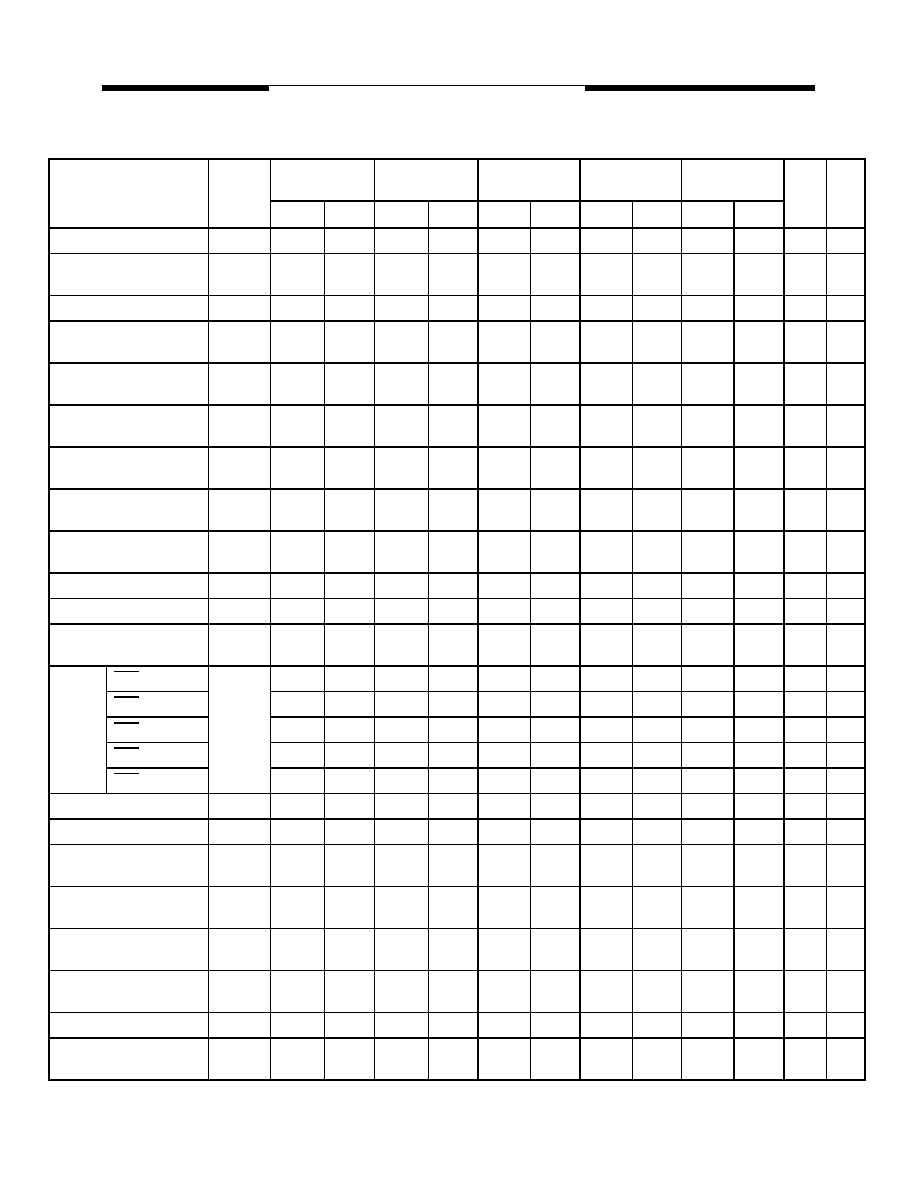

AC Characteristics (AC operating conditions unless otherwise noted)

Parameter

Symbol

(DDR2-533)

-37

(DDR2-667)

-3

(DDR2-800)

-25A

(DDR2-800)

-25

(DDR2-1066)

-19A

Unit Note

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

Row Cycle Time

tRC

60

-

60

-

60

-

57.5

-

58.125

-

ns

Auto Refresh Row Cycle

Time

tRFC

127.5

-

127.5

-

127.5

-

127.5

-

127.5

-

ns

11

Row Active Time

tRAS

45

70K

45

70K

45

70K

45

70K

45

70K

ns

21

Row Address to Column Ad-

dress Delay

tRCD

15

-

15

-

15

-

12.5

-

13.125

-

ns

20

Row Active to Row Active

Delay (x4 & x8)

tRRD

7.5

-

7.5

-

7.5

-

7.5

-

7.5

-

ns

Row Active to Row Active

Delay (x16)

tRRD

10

-

10

-

10

-

10

-

10

-

ns

Four Activate Window for (x4

& x8)

tFAW

37.5

-

37.5

-

35

-

35

-

35

-

ns

Four Active to Row Active

Delay (x16)

tFAW

50

-

50

-

45

-

45

-

45

-

ns

Column Address to Column

Address Delay

tCCD

2

-

2

-

2

-

2

-

2

-

CLK

Row Precharge Time

tRP

15

-

15

-

15

-

12.5

-

13.125

-

ns

Write Recovery Time

tWR

15

-

15

-

15

-

15

-

15

-

ns

Auto Precharge Write Re-

covery + Precharge Time

tDAL

tWR +tRP

-

tWR +tRP

-

tWR +tRP

-

tWR +tRP

-

tWR +tRP

-

ns

12

System

Clock

Cycle

Time

CAS Latency = 3

tCK

5

8

5

8

------

ns

2

CAS Latency = 4

3.75

8

3.75

8

3.75

8

3.75

8

-

ns

2

CAS Latency = 5

-

3

8

3

8

2.5

8

3

8

ns

2

CAS Latency = 6

-

2.5

8

2.5

8

2.5

8

ns

2

CAS Latency = 7

-

----

1.875

8

ns

2

Clock High Level Width

tCH

0.45

0.55

0.48

0.52

0.48

0.52

0.48

0.52

0.48

0.52

CLK

Clock Low Level Width

tCL

0.45

0.55

0.48

0.52

0.48

0.52

0.48

0.52

0.48

0.52

CLK

Data-Out edge to Clock

edge Skew

tAC

-0.5

0.45

-0.45

0.45

-0.40

0.40

-0.40

0.40

-0.35

0.35

ns

DQS-Out edge to Clock

edge Skew

tDQSCK

-0.45

0.40

-0.40

0.40

-0.35

0.35

-0.35

0.35

-0.325

0.325

ns

DQS-Out edge to Data-Out

edge Skew

tDQSQ

-

0.30

-

0.24

-

0.20

-

0.20

-

0.175

ns

Data-Out hold time from

DQS

tQH

tHPmin

-tQHS

-

tHPmin

-tQHS

-

tHPmin

-tQHS

-

tHPmin

-tQHS

-

tHPmin

-tQHS

-

ns

Data hold skew factor

tQHS

-

400

-

340

-

300

-

300

-

250

ps

Clock Half Period

tHP

tCH/L

min

-

tCH/L

min

-

tCH/L

min

-

tCH/L

min

-

tCH/L

min

-

ns

5

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| V59C1G01408QAUP25A | 256M X 4 DDR DRAM, PBGA68 |

| V59C1512164QALJ25AH | 32M X 16 DDR DRAM, PBGA92 |

| V59C1512164QALP37I | 32M X 16 DDR DRAM, PBGA92 |

| V59C1512164QAUJ5I | 32M X 16 DDR DRAM, PBGA92 |

| V59C1512164QAUP19AH | 32M X 16 DDR DRAM, PBGA92 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| V5A010CB | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 PIN PLUNGER |

| V5A010CB | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 PIN PLUNGER |

| V5A010CB4D | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 ROLLER LEVER |

| V5A010CB4D | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 ROLLER LEVER |

| V5A010CB4E | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 ROLLER LEVER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。