- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361602 > UT7R995-XCA (Aeroflex Inc.) RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer PDF資料下載

參數(shù)資料

| 型號: | UT7R995-XCA |

| 廠商: | Aeroflex Inc. |

| 英文描述: | RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

| 中文描述: | RadHard 2.5V/3.3V的200MHz的高速多相PLL時(shí)鐘緩沖器 |

| 文件頁數(shù): | 4/22頁 |

| 文件大小: | 185K |

| 代理商: | UT7R995-XCA |

4

Notes:

1. These outputs are undivided copies of the VCO clock. Therefore, the formulas in this column can be used to calculate the nominal VCO operating frequency (f

NOM

)

at a given reference frequency (f

XTAL

) and the divider and feedback configuration. The user must select a configuration and a reference frequency that will generate

a VCO frequency that is within the range specified by FS pin. Please see Table 7.

1.2 Frequency Range and Skew Selection:

The PLL in the UT7R995/C operates within three nominal fre-

quency ranges. Depending upon the desired PLL operating fre-

quency, the user must define the state of the ternary FS control

pin. Table 7 defines the required FS selections based upon the

nominal PLL operating frequency ranges. Because the clock

outputs on Bank 1 and Bank 2 do not include a divider option,

they will always reflect the current frequency of the PLL. Ref-

erence the first column of equations in Table 6 to calculate the

value of f

NOM

for any given feedback clock.

Selectable output skew is in discrete increments of time unit

(t

U

). The value of t

U

is determined by the FS setting and the

PLL’s operating frequency (f

NOM

). Use the following equation

to calculate the time unit (t

U

):

The f

NOM

term, which is calculated with the help of Table 6,

must be compatible with the nominal frequency range selected

by the FS signal as defined in Table 7. The multiplication factor

(MF), also determined by FS, is shown in Table 8. The

UT7R995/C output skew steps have a typical accuracy of +/-

15% of the calculated time unit (t

U

).

After calculating the time unit (t

U

) based on the nominal PLL

frequency (f

NOM

) and multiplication factor (MF), the circuit

designer plans routing requirements of each clock output and its

respective destination receiver. With an understanding of signal

propagation delays through a conductive medium (see Table 9),

the designer specifies trace lengths which ensure a signal prop-

agation delay that is equal to one of the t

U

multiples show in Ta-

ble 10. For each output bank, the t

U

skew factors are selected

with the tri-level, bank-specific, nF[1:0] pins.

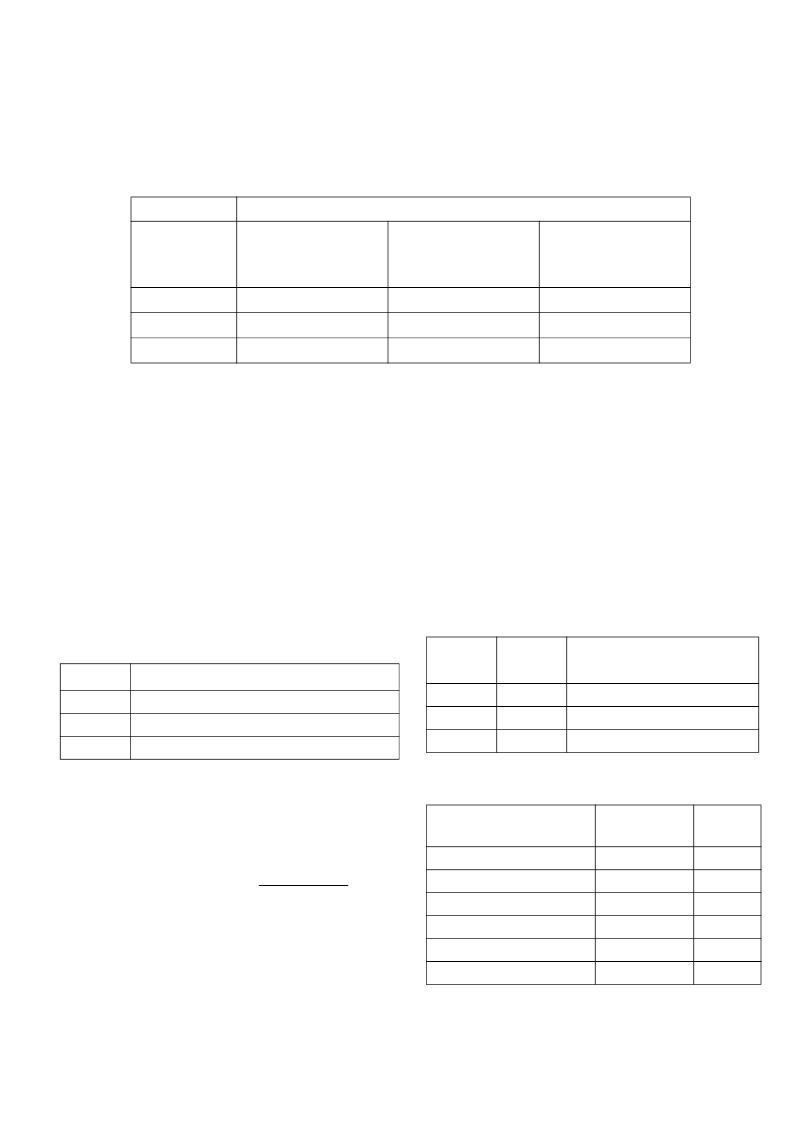

Table 6: Calculating Output Frequency Settings

Configuration

Output Frequency

Clock Output

Connected to FB

1Q[1:0]

1

and

2Q[1:0]

1

3Q[1:0]

4Q[1:0]

1Qn or 2Qn

(N/R) * f

XTAL

(N/R) * (1/K) * f

XTAL

(N/R) * (1/M) * f

XTAL

3Qn

(N/R) * K * f

XTAL

(N/R) * f

XTAL

(N/R) * (K/M) * f

XTAL

4Qn

(N/R) * M * f

XTAL

(N/R) * (M/K) * f

XTAL

(N/R) * f

XTAL

Table 7: Frequency Range Select

FS

Nominal PLL Frequency Range

(f

NOM

)

L

24 to 50 MHz

M

48 to 100MHz

H

96 to 200 MHz

MF)

*

NOM

(f

1

u

t

1.

Equation

=

Table 8: MF Calculation

FS

MF

f

NOM

examples that result

in a t

U

of 1.0ns

L

32

31.25 MHz

M

16

62.5 MHz

H

8

125 MHz

Table 9: Signal Propagation Delays in Various Media

Medium

Propagation

Delay (ps/inch)

Dielectric

Constant

Air (Radio Waves)

85

1.0

Coax. Cable (75% Velocity)

113

1.8

Coax. Cable (66% Velocity)

129

2.3

FR4 PCB, Outer Trace

140 - 180

2.8 - 4.5

FR4 PCB, Inner Trace

180

4.5

Alumina PCB, Inner Trace

240 - 270

8 - 10

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UT7R995-XCC | RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

| UT7R995-XCX | RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

| UT7R995-XPA | RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

| UT7R995-XPC | RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

| UT7R995-XPX | RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UT7R995-XCC | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

| UT7R995-XCX | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

| UT7R995-XPA | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

| UT7R995-XPC | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

| UT7R995-XPX | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。