- 您現在的位置:買賣IC網 > PDF目錄361602 > UT7R995-XCA (Aeroflex Inc.) RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer PDF資料下載

參數資料

| 型號: | UT7R995-XCA |

| 廠商: | Aeroflex Inc. |

| 英文描述: | RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

| 中文描述: | RadHard 2.5V/3.3V的200MHz的高速多相PLL時鐘緩沖器 |

| 文件頁數: | 3/22頁 |

| 文件大小: | 185K |

| 代理商: | UT7R995-XCA |

3

1.0 DEVICE CONFIGURATION:

The outputs of the UT7R995/C can be configured to run at fre-

quencies ranging from 6 MHz to 200 MHz. Each output bank

has the ability to run at separate frequencies and with various

phase skews. Furthermore, numerous clock division and multi-

plication options exist.

The following discussion and list of tables will summarize the

available configuration options for the UT7R995/C. Tables 1

through 12, are relevant to the following configuration discus-

sions.

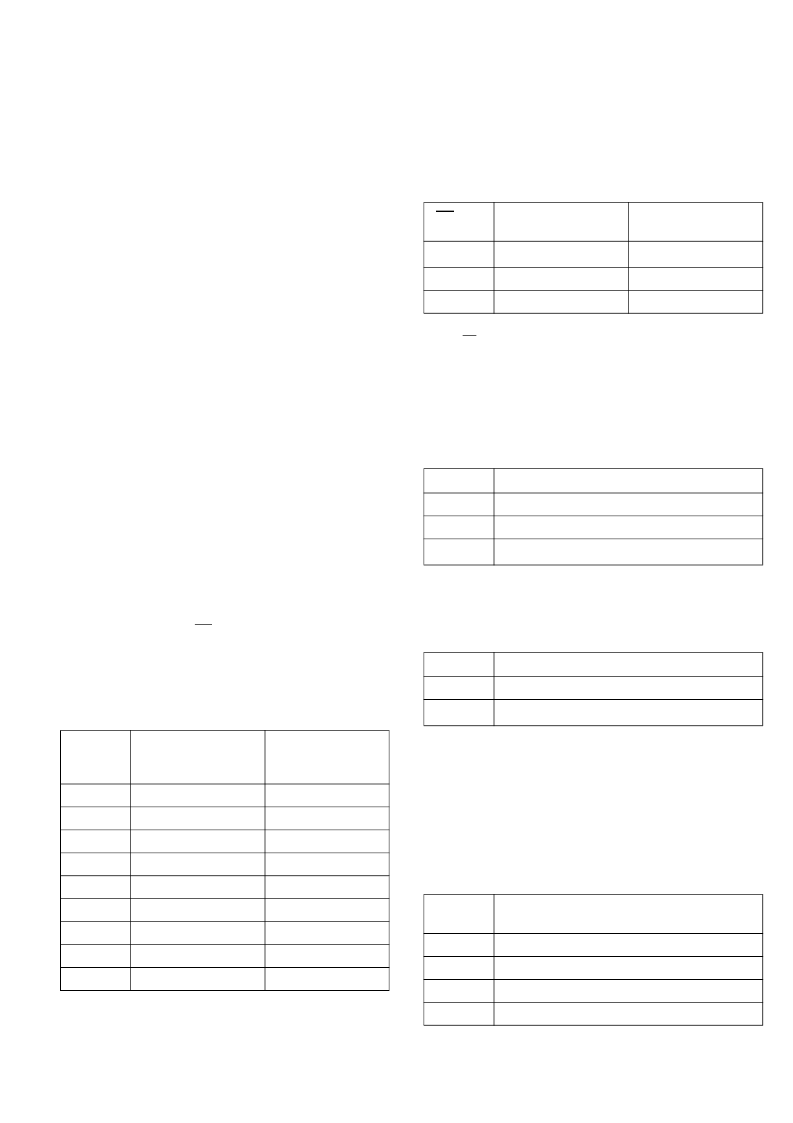

Table 1. Feedback Divider Settings (N-factor)

Table 2. Reference Divider Settings (R-Factor)

Table 3. Output Divider Settings - Bank 3 (K-factor)

Table 4. Output Divider Settings - Bank 4 (M-Factor)

Table 5. Frequency Divider Summary

Table 6. Calculating Output Frequency Settings

Table 7. Frequency Range Select

Table 8. Multiplication Factor (MF) Calculation

Table 9. Signal Propagation Delays in Various Media

Table 10: Output Skew Settings

Table 11. PE/HD Settings

Table 12. Power Supply Constraints

1.1 Divider Configuration Settings:

The feedback input divider is controlled by the 3-level DS[1:0]

pins as indicated in Table 1 and the reference input divider is

controlled by the 3-level PD/DIV pin as indicated in Table 2.

Although the Reference divider will continue to operate when

the UT7R995/C is in the standard TEST mode of operation, the

Feedback Divider will not be available.

Notes:

1. When PD/DIV = LOW, the device enters power-down mode.

In addition to the reference and feedback dividers, the

UT7R995/C includes output dividers on Bank 3 and Bank 4,

which are controlled by 3F[1:0] and 4F[1:0] as indicated in Ta-

bles 3 and 4, respectively.

Notes:

1. These states are used to program the phase of the respective banks. Please see

Equation 1 along with Tables 8 and 10.

Notes:

1. These states are used to program the phase of the respective banks. Please see

Equation 1 along with Tables 8 and 10.

Each of the four divider options and their respective settings are

summarized in Table 5. By applying the divider options in Ta-

ble 5 to the calculations shown in Table 6, the user determines

the proper clock frequency for every output bank.

Table 1: Feedback Divider Settings (

N-factor

)

DS[1:0]

Feedback Input

Divider -

(N)

Permitted Output

Divider (K or M)

Connected to FB

LL

2

1 or 2

LM

3

1

LH

4

1, 2, or 4

ML

5

1 or 2

MM

1

1, 2, or 4

MH

6

1 or 2

HL

8

1 or 2

HM

10

1

HH

12

1

Table 2: Reference Divider Settings (

R-factor

)

PD/DIV

Operating Mode

Reference Input

Divider -

(R)

LOW

1

Powered Down

Not Applicable

MID

Normal Operation

2

HIGH

Normal Operation

1

Table 3: Output Divider Settings - Bank 3 (

K-factor

)

3F(1:0)

Bank 3 Output Divider -

(K)

LL

2

HH

4

Other

1

1

Table 4: Output Divider Settings - Bank 4 (

M-factor

)

4F[1:0]

Bank 4 Output Divider

(M)

LL

2

Other

1

1

Table 5: Frequency Divider Summary

Division

Factors

Available Divider Settings

N

1, 2, 3, 4, 5, 6, 8, 10, 12

R

1, 2

K

1, 2, 4

M

1, 2

相關PDF資料 |

PDF描述 |

|---|---|

| UT7R995-XCC | RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

| UT7R995-XCX | RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

| UT7R995-XPA | RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

| UT7R995-XPC | RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

| UT7R995-XPX | RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

相關代理商/技術參數 |

參數描述 |

|---|---|

| UT7R995-XCC | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

| UT7R995-XCX | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

| UT7R995-XPA | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

| UT7R995-XPC | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

| UT7R995-XPX | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:RadHard 2.5V/3.3V 200MHz High-Speed Multi-phase PLL Clock Buffer |

發(fā)布緊急采購,3分鐘左右您將得到回復。