- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359310 > uPSD3412C-40U6T (意法半導(dǎo)體) 320 x 240 pixel format, CFL backlight available with power harness PDF資料下載

參數(shù)資料

| 型號(hào): | uPSD3412C-40U6T |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | 320 x 240 pixel format, CFL backlight available with power harness |

| 中文描述: | 閃存可編程系統(tǒng)設(shè)備與8032微控制器核心和16Kbit SRAM的 |

| 文件頁(yè)數(shù): | 76/152頁(yè) |

| 文件大小: | 1558K |

| 代理商: | UPSD3412C-40U6T |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)當(dāng)前第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)

UPSD3212C, UPSD3212CV

76/152

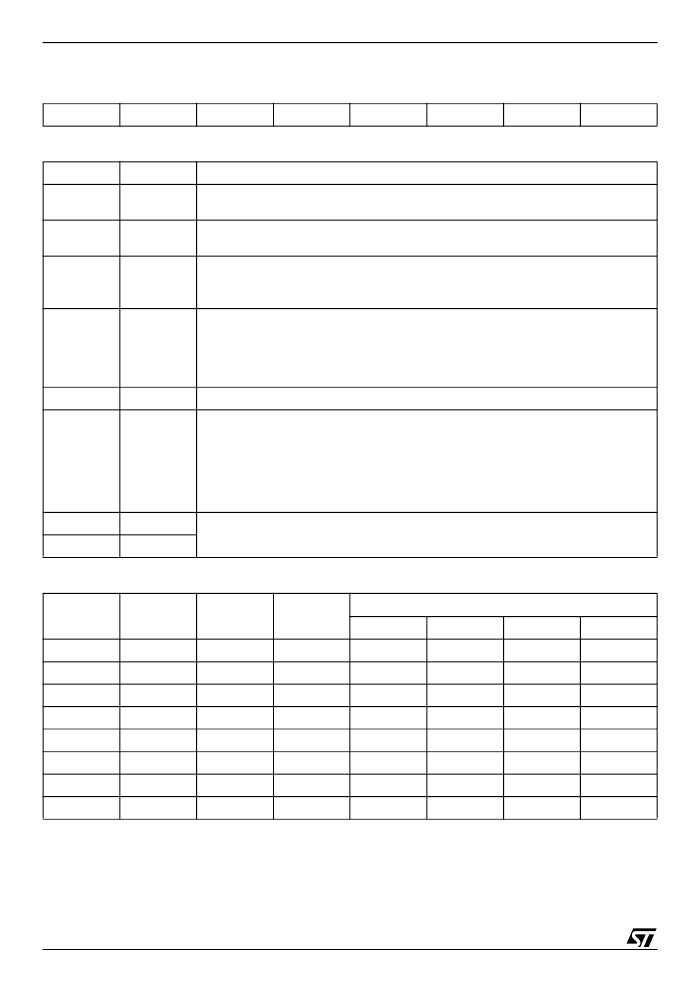

Table 50. Serial Control Register (S2CON)

Table 51. Description of the S2CON Bits

Table 52. Selection of the Serial Clock Frequency SCL in Master Mode

7

6

5

4

3

2

1

0

CR2

ENII

STA

STO

ADDR

AA

CR1

CR0

Bit

Symbol

Function

7

CR2

This bit along with Bits CR1and CR0 determines the serial clock frequency when SIO is

in the Master Mode.

6

ENII

Enable IIC. When ENI1 = 0, the IIC is disabled. SDA and SCL outputs are in the high

impedance state.

5

STA

START Flag. When this bit is set, the SIO H/W checks the status of the I

2

C-bus and

generates a START condition if the bus free. If the bus is busy, the SIO will generate a

repeated START condition when this bit is set.

4

STO

STOP Flag. With this bit set while in Master Mode a STOP condition is generated.

When a STOP condition is detected on the I

2

C bus, the I

2

C hardware clears the STO

Flag.

Note:

This bit have to be set before 1 cycle interrupt period of STOP. That is, if this bit is

set, STOP condition in Master Mode is generated after 1 cycle interrupt period.

3

ADDR

This bit is set when address byte was received. Must be cleared by software.

2

AA

Acknowledge enable signal. If this bit is set, an acknowledge (low level to SDA) is

returned during the acknowledge clock pulse on the SCL line when:

Own slave address is received

A data byte is received while the device is programmed to be a Master Receiver

A data byte is received while the device is a selected Slave Receiver. When this bit is

reset, no acknowledge is returned.

SIO release SDA line as high during the acknowledge clock pulse.

1

CR1

These two bits along with the CR2 Bit determine the serial clock frequency when SIO is

in the Master Mode.

0

CR0

CR2

CR1

CR0

f

OSC

Divisor

Bit Rate (kHz) at f

OSC

12MHz

24MHz

36MHz

40MHz

0

0

0

16

375

750

X

X

0

0

1

24

250

500

750

833

0

1

0

30

200

400

600

666

0

1

1

60

100

200

300

333

1

0

0

120

50

100

150

166

1

0

1

240

25

50

75

83

1

1

0

480

12.5

25

37.5

41

1

1

1

960

6.25

12.5

18.75

20

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPSD3433EV-40U6 | Turbo Plus Series Fast Turbo 8032 MCU with USB and Programmable Logic |

| UR132-26-AE3-5-R | 200mA LOW DROPOUT LINEAR VOLTAGE REGULATOR |

| URS1A101MRD | ALUMINUM ELECTROLYTIC CAPACITORS |

| URU1V470MRD | ALUMINUM ELECTROLYTIC CAPACITORS |

| URZ1A101MPD | ALUMINUM ELECTROLYTIC CAPACITORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPSD3422E-40T6 | 功能描述:8位微控制器 -MCU 8 BITS MICROCONTR RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| UPSD3422E-40U6 | 功能描述:8位微控制器 -MCU 8 BITS MICROCONTR RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| UPSD3422EB40T6 | 功能描述:8位微控制器 -MCU Turbo 8032 MCU w/USB & Programmable Logic RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| UPSD3422EB40U6 | 功能描述:8位微控制器 -MCU uPSD34x Turbo Plus Fast Turbo 8032 MCU RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| UPSD3422EV-40T6 | 功能描述:8位微控制器 -MCU 8 BITS MICROCONTR RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。