- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382721 > UDA1350ATS (NXP SEMICONDUCTORS) IEC 958 audio DAC PDF資料下載

參數(shù)資料

| 型號: | UDA1350ATS |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | IEC 958 audio DAC |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

| 封裝: | PLASTIC, SSOP-28 |

| 文件頁數(shù): | 9/32頁 |

| 文件大小: | 124K |

| 代理商: | UDA1350ATS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

2000 Mar 29

9

Philips Semiconductors

Preliminary specification

IEC 958 audio DAC

UDA1350ATS

The extracted key parameters are:

Pre-emphasis

Audio sample frequency

Two-channel PCM indicator

Clock accuracy.

Both the lock indicator and the key channel status bits are

accessible via the L3 interface.

The UDA1350ATS supports the following sample

frequencies and data bit rates:

f

s

= 32.0 kHz, resulting in a data rate of 2.048 Mbits/s

f

s

= 44.1 kHz, resulting in a data rate of 2.8224 Mbits/s

f

s

= 48.0 kHz, resulting in a data rate of 3.072 Mbits/s.

The UDA1350ATS supports timing level I, II and III as

specified by the IEC 958 standard.

8.4.2

A

UDIO FEATURE PROCESSOR

The audio feature processor automatically provides

de-emphasis for the IEC 958 data stream in the static pin

control mode and default mute at start-up in the L3 control

mode.

When used in the L3 control mode it provides the following

additional features:

Volume control using 6 bits

Bass boost control using 4 bits

Treble control using 2 bits

Mode selection of the sound processing bass boost and

treble filters: flat, minimum and maximum

Soft mute control with raised cosine roll-off

De-emphasis selection of the incoming data stream for

f

s

= 32.0, 44.1 and 48.0 kHz.

8.4.3

I

NTERPOLATOR

TheUDA1350ATSincludesanon-boardinterpolatingfilter

which converts the incoming data stream from 1f

s

to 128f

s

by cascading a recursive filter and a FIR filter.

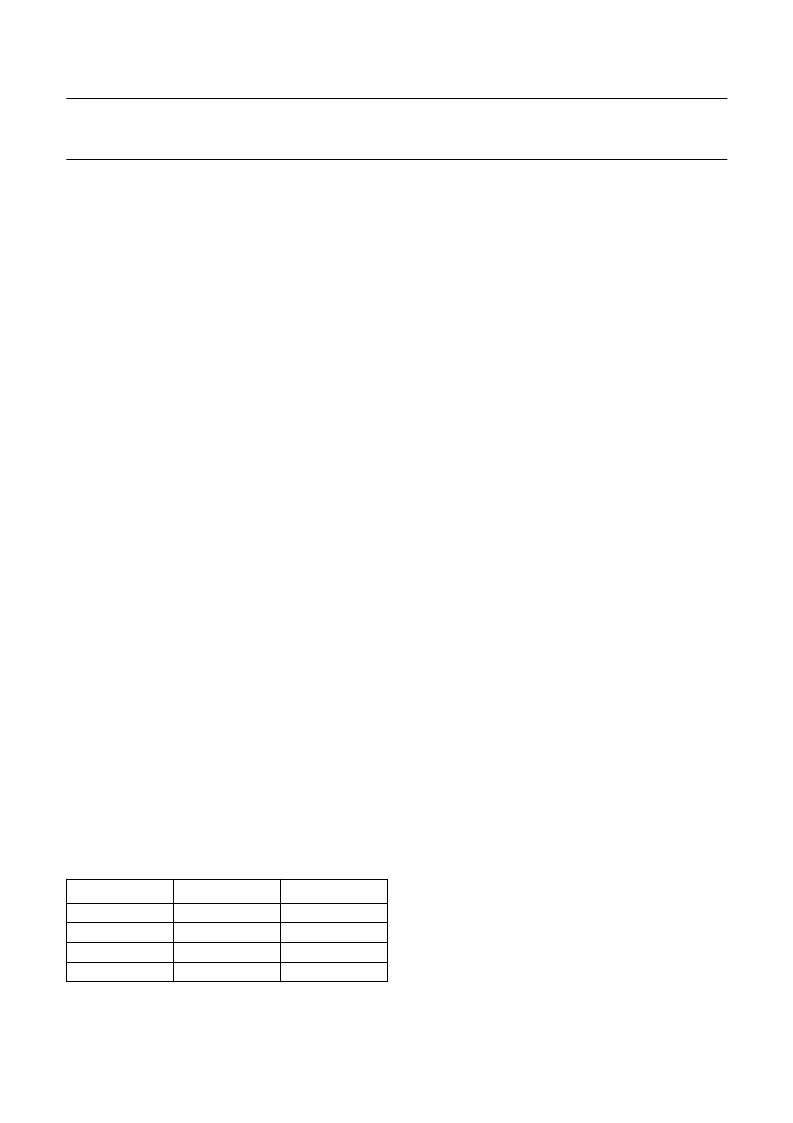

Table 2

Interpolator characteristics

8.4.4

N

OISE SHAPER

The third-order noise shaper operates at 128f

s

. It shifts

in-band quantization noise to frequencies well above the

audio band. This noise shaping technique enables high

signal-to-noise ratios to be achieved. The noise shaper

output is converted into an analog signal using a filter

stream digital-to-analog converter.

8.4.5

F

ILTER STREAM

DAC

The Filter Stream DAC (FSDAC) is a semi-digital

reconstruction filter that converts the 1-bit data stream of

the noise shaper to an analog output voltage. The filter

coefficients are implemented as current sources and are

summed at virtual ground of the output operational

amplifier. In this way very high signal-to-noise

performance and low clock jitter sensitivity is achieved. A

post filter is not needed due to the inherent filter function of

the DAC. On-board amplifiers convert the FSDAC output

current to an output voltage signal capable of driving a line

output.

The output voltage of the FSDAC is scaled proportionally

with the power supply voltage.

8.5

Control

The UDA1350ATS can be controlled by means of static

pins or via the L3 interface. For optimum use of the

features of the UDA1350ATS the L3 control mode is

recommended since only basic functions are available in

the static pin control mode.

It should be noted that the static pin control mode and

L3 control mode are mutual exclusive. In the static pin

control mode pins L3MODE and L3DATA are used to

select the format for the data output and input interface.

PARAMETER

CONDITIONS

VALUE (dB)

±

0.03

50

115

3.5

Pass-band ripple

Stop band

Dynamic range

DC gain

0 to 0.45f

s

>0.65f

s

0 to 0.45f

s

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UDA1351 | 96 kHz IEC 958 audio DAC |

| UDA1351H | 96 kHz IEC 958 audio DAC |

| UDA1351TS | 96 kHz IEC 958 audio DAC |

| UDA1352HL | 48 kHz IEC 60958 audio DAC |

| UDA1360 | Low-voltage low-power stereo audio ADC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UDA1351 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:96 kHz IEC 958 audio DAC |

| UDA1351H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:96 kHz IEC 958 audio DAC |

| UDA1351H/N1,551 | 功能描述:數(shù)模轉(zhuǎn)換器- DAC 96 KHZ SPDIF DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時(shí)間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| UDA1351H/N1,557 | 功能描述:數(shù)模轉(zhuǎn)換器- DAC 96 KHZ SPDIF DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時(shí)間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| UDA1351TS | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:96 kHz IEC 958 audio DAC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。