- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄382707 > U630H64DK45 NVRAM (EEPROM Based) PDF資料下載

參數(shù)資料

| 型號(hào): | U630H64DK45 |

| 英文描述: | NVRAM (EEPROM Based) |

| 中文描述: | NVRAM中(EEPROM的基礎(chǔ)) |

| 文件頁(yè)數(shù): | 5/14頁(yè) |

| 文件大?。?/td> | 143K |

| 代理商: | U630H64DK45 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)

5

November 01, 2001

U630H64

High Impedance

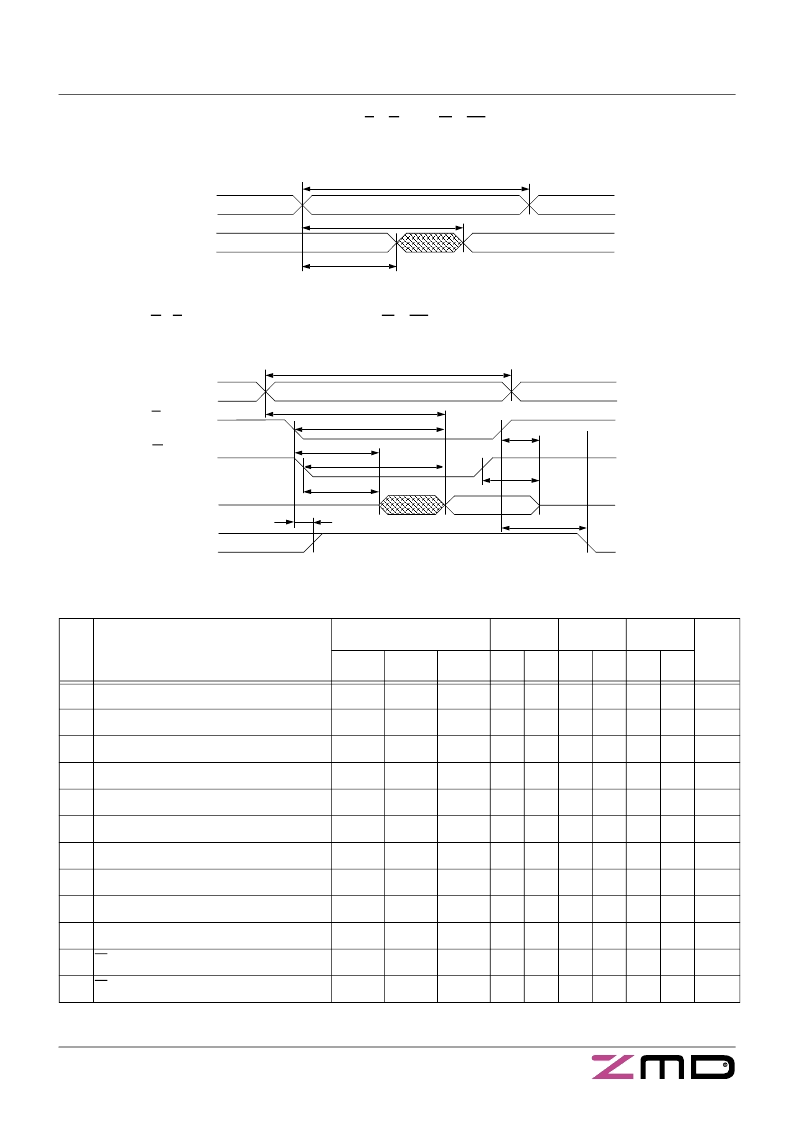

Read Cycle 1: Ai-controlled (during Read cycle: E = G = V

IL

, W = NE = V

IH

)

f

t

a(A)

Previous Data Valid

Output Data Valid

t

cR

Address Valid

t

v(A)

Ai

DQi

Output

Read Cycle 2: G-, E-controlled (during Read cycle: W = NE = V

IH

)

g

Ai

E

G

t

dis(E)

t

cR

t

a(E)

t

en(E)

t

en(G)

t

a(G)

t

dis(G)

Address Valid

t

a(A)

(2)

Output Data Valid

I

CC

ACTIVE

STANDBY

t

PD

t

PU

No.Switching Characteristics

Write Cycle

Symbol

25

35

45

Unit

Alt. #1

Alt. #2

IEC

Min. Max. Min. Max. Min. Max.

12 Write Cycle Time

t

AVAV

t

AVAV

t

cW

25

35

45

ns

13 Write Pulse Width

t

WLWH

t

w(W)

20

30

35

ns

14 Write Pulse Width Setup Time

t

WLEH

t

su(W)

20

30

35

ns

15 Address Setup Time

t

AVWL

t

AVEL

t

su(A)

0

0

0

ns

16 Address Valid to End of Write

t

AVWH

t

AVEH

t

su(A-WH)

20

30

35

ns

17 Chip Enable Setup Time

t

ELWH

t

su(E)

20

30

35

ns

18 Chip Enable to End of Write

t

ELEH

t

w(E)

20

30

35

ns

19 Data Setup Time to End of Write

t

DVWH

t

DVEH

t

su(D)

12

18

20

ns

20 Data Hold Time after End of Write

t

WHDX

t

EHDX

t

h(D)

0

0

0

ns

21 Address Hold after End of Write

t

WHAX

t

EHAX

t

h(A)

0

0

0

ns

22 W LOW to Output in High-Z

h, i

t

WLQZ

t

dis(W)

10

13

15

ns

23 W HIGH to Output in Low-Z

t

WHQX

t

en(W)

5

5

5

ns

(1)

(2)

(9)

(1)

(3)

(4)

(5)

(7)

(6)

(8)

10

(11)

DQi

Output

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| U630H64SC25 | Low noise JFET quad operational amplifier |

| U630H64SC35 | Low noise JFET quad operational amplifier |

| U630H64SC45 | NVRAM (EEPROM Based) |

| U630H64SK25 | Low noise JFET quad operational amplifier |

| U630H64SK35 | NVRAM (EEPROM Based) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| U630H64SC25 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:NVRAM (EEPROM Based) |

| U630H64SC35 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:NVRAM (EEPROM Based) |

| U630H64SC45 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:NVRAM (EEPROM Based) |

| U630H64SK25 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:NVRAM (EEPROM Based) |

| U630H64SK35 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:NVRAM (EEPROM Based) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。