- 您現(xiàn)在的位置:買賣IC網 > PDF目錄297620 > TSPC603RMY12LC (ATMEL CORP) 32-BIT, 266 MHz, RISC PROCESSOR, MQFP240 PDF資料下載

參數(shù)資料

| 型號: | TSPC603RMY12LC |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 266 MHz, RISC PROCESSOR, MQFP240 |

| 封裝: | CAVITY UP, METAL, QFP-240 |

| 文件頁數(shù): | 5/40頁 |

| 文件大小: | 670K |

| 代理商: | TSPC603RMY12LC |

第1頁第2頁第3頁第4頁當前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

TSPC603r

in CERQUAD and MQUAD Packages

13/40

3.6.1. Dynamic Power Management

Dynamic power management automatically powers up and down the individual execution units of the 603r, based upon the contents

of the instruction stream. For example, if no floating-point instructions are being executed, the floating-point unit is automatically pow-

ered down. Power is not actually removed from the execution unit ; instead, each execution unit has an independent clock input, which

is automatically controlled on a clock-by- clock basis. Since CMOS circuits consume negligible power when they are not switching,

stopping the clock to an execution unit effectively eliminates its power consumption. The operation of DPM is completely transparent

to software or any external hardware. Dynamic power management is enabled by setting bit 11 in HID0 on power-up, of following

HRESET.

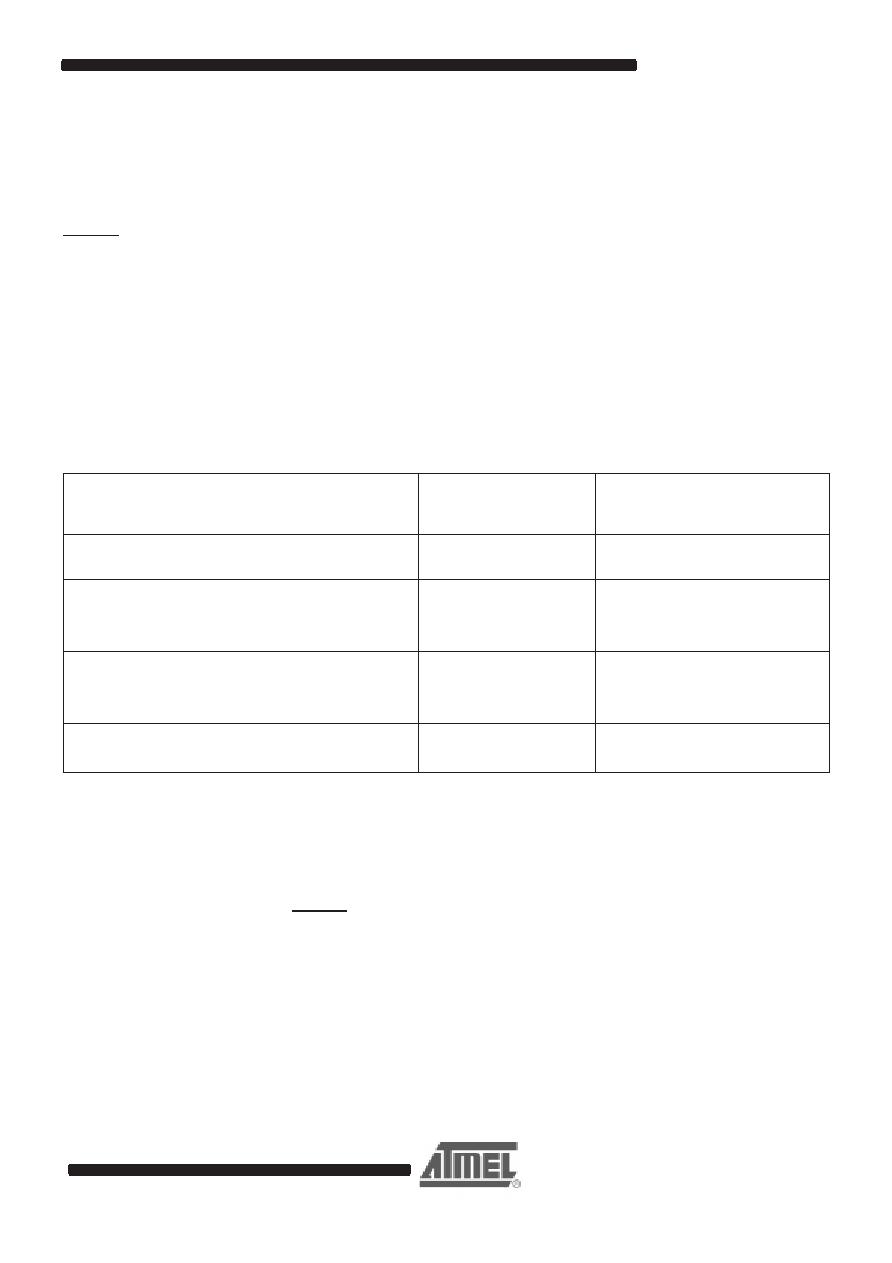

3.6.2. Programmable Power Modes

The 603r provides four programmable power states - full power, doze, nap and sleep. Software selects these modes by setting one

(and only one) of the three power saving mode bits. Hardware can enable a power management state through external asynchronous

interrupts The hardware interrupt causes the transfer of program flow to interrupt handler code. The appropriate mode is then set by

the software. The 603r provides a separate interrupt and interrupt vector for power management - the system management interrupt

(SMI). The 603r also contains a decrement timer which allows it to enter the nap or doze mode for a predetermined amount of time and

then return to full power operation through the decrementer interrupt (DI). Note that the 603r cannot switch from on power manage-

ment mode to another without first returning to full on mode. The nap and sleep modes disable bus snooping ; therefore, a hardware

handshake is provided to ensure coherency before the 603r enters these power management modes. AUCUN LIEN summarizes

the four power states.

Table 6.Power PC 603r Microprocessor Programmable Power Modes

PM Mode

Functioning Units

Activation Method

Full-Power Wake Up Method

Full power

All units active

–

Full power (with DPM)

Requested logic by

demand

By instruction dispatch

–

Doze

- Bus snooping

- Data cache as needed

- Decrementer timer

Controlled by SW

External asynchronous exceptions*

Decrementer interrupt

Reset

Nap

Decrementer timer

Controlled by hardware and

software

External asynchronous exceptions

Decrementer interrupt

Reset

Sleep

None

Controlled by hardware and

software

External asynchronous exceptions

Reset

* Exceptions are referred to as interrupts in the architecture specification

3.6.3. Power Management Modes

The following sections describe the characteristics of the 603r’s power management modes, the requirements for entering and exiting

the various modes, and the system capabilities provided by the 603r while the power management modes are active.

1.

Full-Power Mode with DPM Disabled

Full-power mode with DPM disabled power mode is selected when the DPM enable bit (bit 11) in HID0 is cleared.

- Default state following power-up and HRESET.

- All functional units are operating at full processor speed at all times.

2.

Full-Power Mode with DPM Enabled

Full-power mode with DPM enabled (HID0[11] = 1) provides on-chip power management without affecting the functionality or perfor-

mance of the 603r.

- Required functional units are operating at full processor speed.

- Functional units are clocked only when needed.

- No software or hardware intervention required after mode is set.

- Software/hardware and performance transparent.

3.

Doze Mode

Doze ode disables most functional units but maintains cache coherency by enabling the bus interface unit and snooping. A snoop hit

will cause the 603r to enable the data cache, copy the data back to memory, disable the cache, and fully return to the doze state.

相關PDF資料 |

PDF描述 |

|---|---|

| TSZ8G47S | TRIGGER OUTPUT SOLID STATE RELAY, 2060 V ISOLATION-MAX |

| TT11DGRA1 | TOGGLE SWITCH, SPDT, LATCHED, THROUGH HOLE-RIGHT ANGLE |

| TT13A3T | TOGGLE SWITCH, SPST, LATCHED, 3A, PANEL MOUNT-THREADED |

| TT21NGPC9T1/4 | TOGGLE SWITCH, DPDT, LATCHED, THROUGH HOLE-STRAIGHT |

| TV01RW-9-35S | 6 CONTACT(S), METAL, FEMALE, MIL SERIES CONNECTOR, CRIMP, RECEPTACLE |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TSPC603RVA8LC | 功能描述:IC MPU 32BIT 8MHZ 240CERQUAD RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標準包裝:60 系列:SCC 處理器類型:Z380 特點:全靜電 Z380 CPU 速度:20MHz 電壓:5V 安裝類型:表面貼裝 封裝/外殼:144-LQFP 供應商設備封裝:144-LQFP 包裝:托盤 |

| TSPC603RVAB/Q8L | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:PowerPC 603e RISC Microprocessor Family PID7t-603e |

| TSPC603RVAB/Q8LC | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:PowerPC 603e RISC Microprocessor Family PID7t-603e |

| TSPC603RVG10LC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|CERAMIC |

| TSPC603RVG12LC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|CERAMIC |

發(fā)布緊急采購,3分鐘左右您將得到回復。