- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98300 > TS8388BVGL (E2V TECHNOLOGIES PLC) 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CBGA68 PDF資料下載

參數(shù)資料

| 型號: | TS8388BVGL |

| 廠商: | E2V TECHNOLOGIES PLC |

| 元件分類: | ADC |

| 英文描述: | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CBGA68 |

| 封裝: | 1.27 MM PITCH, CERAMIC, BGA-68 |

| 文件頁數(shù): | 4/62頁 |

| 文件大?。?/td> | 1267K |

| 代理商: | TS8388BVGL |

第1頁第2頁第3頁當前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁

12

0860E–BDC–05/07

TS8388B

e2v semiconductors SAS 2007

5.7

Digital Output Coding

NRZ (Non Return to Zero) mode, ideal coding: does not include gain, offset, and linearity voltage errors.

6.

Package Description

6.1

Pin Description

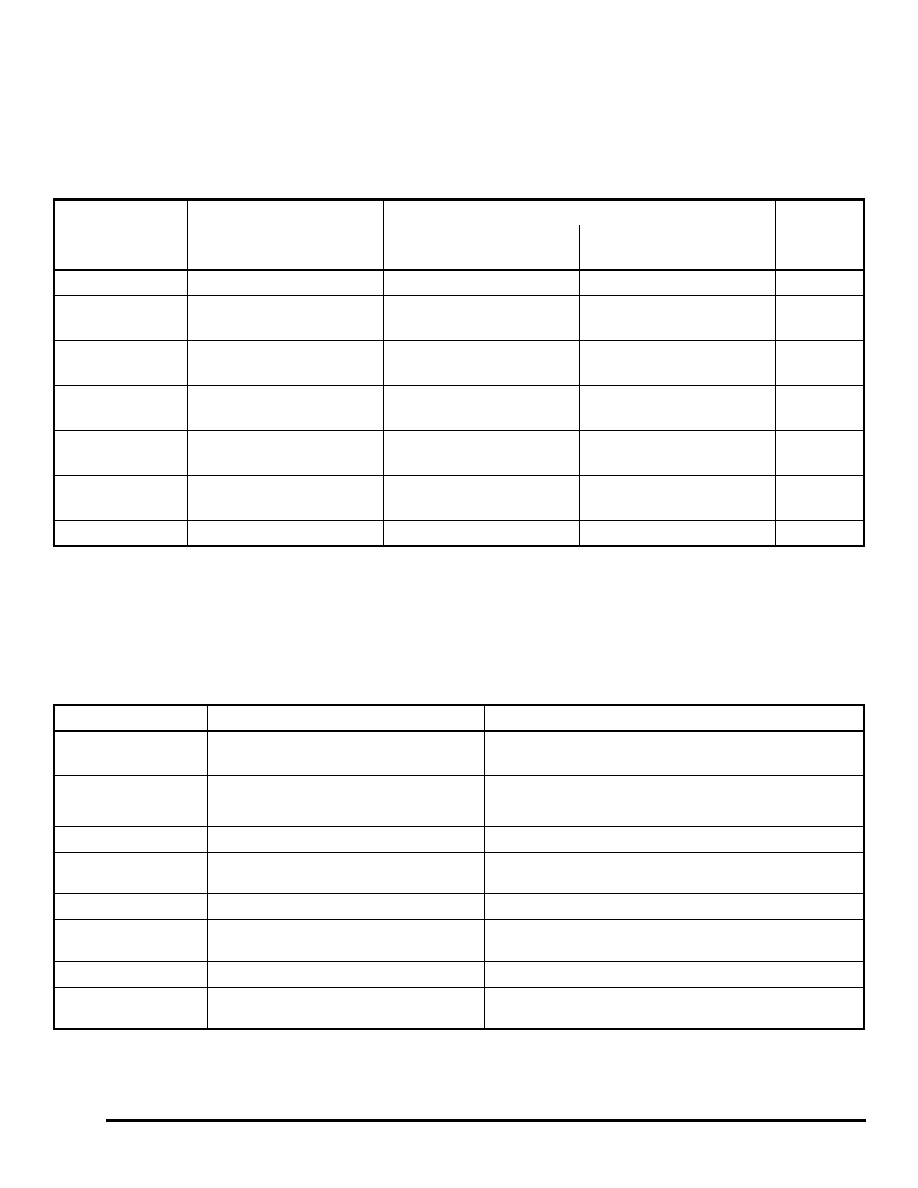

Table 5-6.

Digital Output Coding

Differential

Analog Input

Voltage Level

Digital Output

Out-of

Range

Binary

GORB = VCC or Floating

Gray

GORB = GND

> +251 mV

> Positive full scale + 1/2 lsb

1 1 1 1 1 1 1 1

1 0 0 0 0 0 0 0

1

+251 mV

+249 mV

Positive full scale + 1/2 lsb

Positive full scale – 1/2 lsb

1 1 1 1 1 1 1 1

1 1 1 1 1 1 1 0

1 0 0 0 0 0 0 0

1 0 0 0 0 0 0 1

0

+126 mV

+124 mV

Positive 1/2 scale + 1/2 lsb

Positive 1/2 scale – 1/2 lsb

1 1 0 0 0 0 0 0

1 0 1 1 1 1 1 1

1 0 1 0 0 0 0 0

1 1 1 0 0 0 0 0

0

+1 mV

–1 mV

Bipolar zero + 1/2 lsb

Bipolar zero – 1/2 lsb

1 0 0 0 0 0 0 0

0 1 1 1 1 1 1 1

1 1 0 0 0 0 0 0

0 1 0 0 0 0 0 0

0

–124 mV

–126 mV

Negative 1/2 scale + 1/2 lsb

Negative 1/2 scale – 1/2 lsb

0 1 0 0 0 0 0 0

0 0 1 1 1 1 1 1

0 1 1 0 0 0 0 0

0 0 1 0 0 0 0 0

0

–249 mV

–251 mV

Negative full scale + 1/2 lsb

Negative full scale – 1/2 lsb

0 0 0 0 0 0 0 1

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 1

0 0 0 0 0 0 0 0

0

< –251 mV

< Negative full scale – 1/2 lsb

0 0 0 0 0 0 0 0

1

Table 6-1.

TS8388BGL Pin Description (CBGA68 Package)

Symbol

Pin number

Function

GND

A2, A5, B1, B5, B10, C2, D2, E1, E2, E11,

F1, F2, G11, K2, K3, K4, K5, K10, L2, L5

Ground pins.

To be connected to external ground plane.

VCC

A4, A6, B2, B4, B6, H1, H2, L6, L7

+5V positive supply.

V

EE

A3, B3, G1, G2, J1, J2

5V analog negative supply.

DV

EE

F10, F11

–5V digital negative supply.

V

IN

L3

In phase (+) analog input signal of the Sample and Hold

differential preamplifier.

V

INB

L4

Inverted phase (-) of ECL clock input signal (CLK).

CLK

C1

In phase (+) ECL clock input signal. The analog input is

sampled and held on the rising edge of the CLK signal.

CLKB

D1

Inverted phase (-) of ECL clock input signal (CLK).

B0, B1, B2, B3, B4,

B5, B6, B7

A8, A9, A10, D10, H11, J11, K9, K8

In phase (+) digital outputs.

B0 is the LSB. B7 is the MSB.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TS8388BMFSB/T | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| TS8388BVFS | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| TS8388BMF | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| TS8388BCFS | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| TS8388BCF | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TS8388BVGL (+LID) | 制造商:e2v technologies 功能描述:ADC 8-BIT 1 GSPS - Trays |

| TS83C194 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microcontroller |

| TS83C196KB-10 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microcontroller |

| TS83C196KD | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| TS83C196KD20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。