- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368655 > TMP93CM40A Microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | TMP93CM40A |

| 英文描述: | Microcontroller |

| 中文描述: | 微控制器 |

| 文件頁(yè)數(shù): | 8/16頁(yè) |

| 文件大?。?/td> | 131K |

| 代理商: | TMP93CM40A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)

TMP93CF76/CF77/CW76/CU76/CT76

93CF76-8

2001-09-07

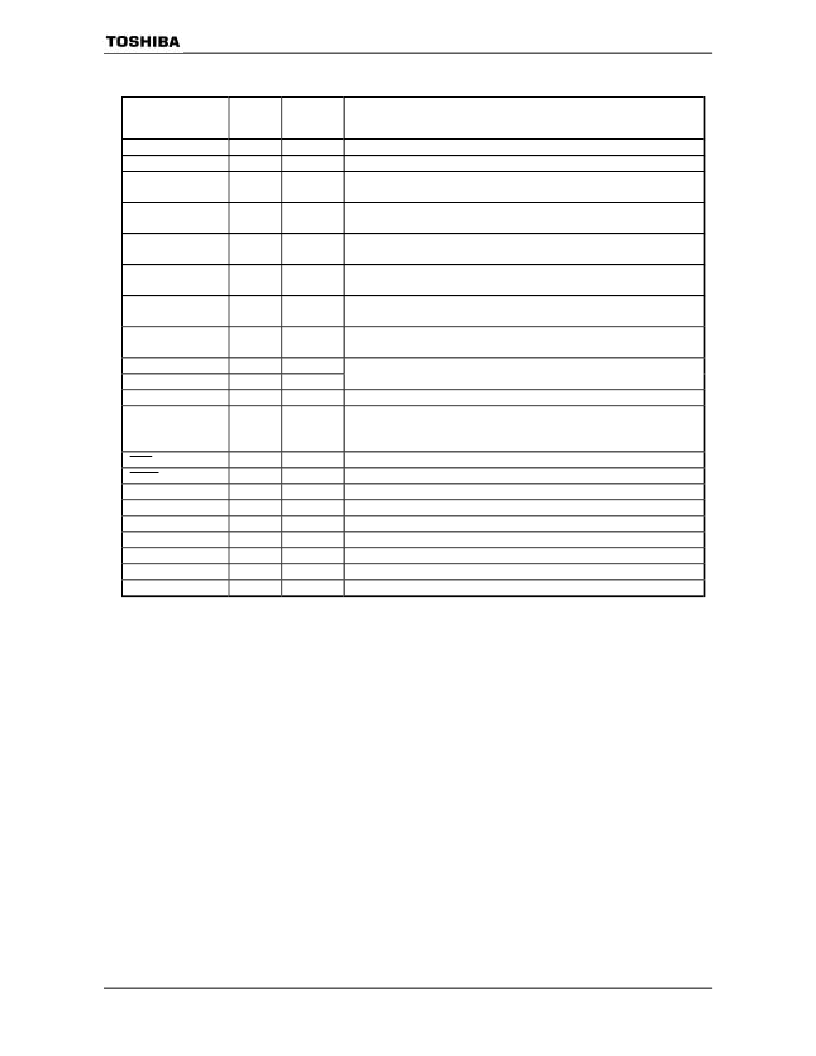

Table 2.2.1 Pin names and function (3/3)

Pin name

Number

of pins

I/O

Functions

PWM0

PWM1

PB0

XT1

PB1

XT2

PC0 to PC7

G0 to G7

PD0,1

G8, 9

PE0 to PE7

S0 to S7

PF0 to PF5

S8 to S13

TEST1

TEST2

TEST3(NC)

CLK

1

1

1

Output

Output

I/O

Input

I/O

Output

Output

Output

Output

Output

I/O

Output

I/O

Output

Output

Input

Output

Output

PWM(14 bits) output 0 (Push-pull or open-drain output selectable)

PWM(14 bits) output 1 (Push-pull or open-drain output selectable)

PortB0: I/O port (Open-drain Output)

Low Frequency Oscillator connecting pin

PortB1: I/O port (Open-drain Output)

Low Frequency Oscillator connecting pin

PortC: Output (High break down voltage outputs with pull-down resistor)

Grid Drivers

PortD: Output (High break down voltage outputs with pull-down resistor)

Grid Drivers

PortE: I/O ports (High break down voltage outputs with pull-down resistor)

Segment Drivers

PortF: I/O ports (High break down voltage outputs with pull-down resistor)

Segment Drivers

1

8

2

8

6

1

1

1

1

TEST1 should be connected with TEST2 pin.

TEST3 should be open connection.

Clock output: Output (System Clock

÷

2) clock.

Pulled-up during reset.

Can be set to output disable for reducing noise. (Initial Disable)

Test pin: Always set to “Vcc” level

Reset: Initializes LSI. (with pull-up resistor)

High Frequency Oscillator connecting pins (16 MHz)

High Frequency Oscillator connecting pins (16 MHz)

VFT Driver power supply pin

Power supply pin

GND pin (0 V)

Reference voltage input for AD converter

GND pin for AD converter

TEST

1

1

1

1

1

1

1

1

1

Input

Input

Input

Output

RESET

X1

X2

VKK

DVCC

DGND

ADREF

ADGND

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMP93CM41A | Microcontroller |

| TMP93CM41F | 16-Bit Microcontroller |

| TMP93CM84F | 16-Bit Microcontroller |

| TMP93CS40 | Microcontroller |

| TMP93CT75F | Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMP93CM40F | 制造商:Toshiba America Electronic Components 功能描述:32KROM, 2KRAM, 900/L - Tape and Reel |

| TMP93CM41A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| TMP93CM41F | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microcontroller |

| TMP93CM41FG(BZ) | 制造商:Toshiba America Electronic Components 功能描述: |

| TMP93CM84F | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。