- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384024 > TMP320C6205ZHKA200 (Texas Instruments, Inc.) FIXED-POINT DIGITAL SIGNAL PROCESSOR PDF資料下載

參數(shù)資料

| 型號(hào): | TMP320C6205ZHKA200 |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 數(shù)字信號(hào)處理 |

| 英文描述: | FIXED-POINT DIGITAL SIGNAL PROCESSOR |

| 中文描述: | 定點(diǎn)數(shù)字信號(hào)處理器 |

| 文件頁(yè)數(shù): | 30/72頁(yè) |

| 文件大小: | 1143K |

| 代理商: | TMP320C6205ZHKA200 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)當(dāng)前第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)

SPRS106G OCTOBER 1999 REVISED JULY 2006

30

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

triggering, wake-up, and effects

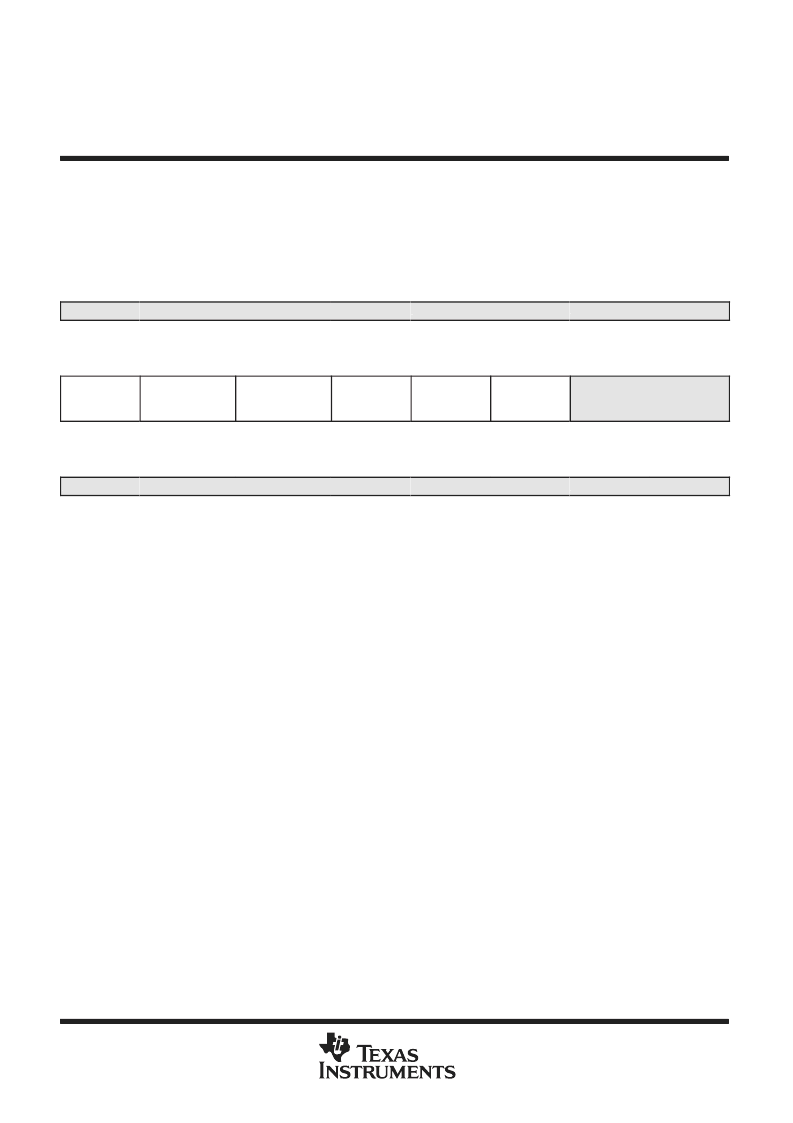

The power-down modes and their wake-up methods are programmed by setting the PWRD field (bits 1510)

of the control status register (CSR). The PWRD field of the CSR is shown in Figure 8 and described in Table 5.

When writing to the CSR, all bits of the PWRD field should be set at the same time. Logic 0 should be used when

“writing” to the reserved bit (bit 15) of the PWRD field. The CSR is discussed in detail in the

TMS320C6000 CPU

and Instruction Set Reference Guide

(literature number SPRU189).

31

16

15

14

13

12

11

10

9

8

Reserved

Enable or

Non-Enabled

Interrupt Wake

Enabled

Interrupt Wake

PD3

PD2

PD1

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

7

0

Legend:

R/Wx = Read/write reset value

NOTE: The shadowed bits are not part of the power-down logic discussion and therefore are not covered here. For information on these other

bit fields in the CSR register, see the

TMS320C6000 CPU and Instruction Set Reference Guide

(literature number SPRU189).

Figure 8. PWRD Field of the CSR Register

Power-down mode PD1 takes effect eight to nine clock cycles after the instruction that sets the PWRD bits in the

CSR.

If PD1 mode is terminated by a non-enabled interrupt, the program execution returns to the instruction where PD1

took effect. If PD1 mode is terminated by an enabled interrupt, the interrupt service routine will be executed first,

then the program execution returns to the instruction where PD1 took effect. The GIE bit in CSR and the NMIE

bit in the interrupt enable register (IER) must also be set in order for the interrupt service routine to execute;

otherwise, execution returns to the instruction where PD1 took effect upon PD1 mode termination by an enabled

interrupt.

PD2 and PD3 modes can only be aborted by device reset. Table 5 summarizes all the power-down modes.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMX320DM6446ZWT | Digital Media System on-Chip |

| TN28F010-90 | 28F010 1024K (128K X 8) CMOS FLASH MEMORY |

| TN28F010-120 | 28F010 1024K (128K X 8) CMOS FLASH MEMORY |

| TN28F010-150 | 28F010 1024K (128K X 8) CMOS FLASH MEMORY |

| TN28F020-90 | 28F020 2048K (256K X 8) CMOS FLASH MEMORY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMP320C6211BGFN100 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSOR |

| TMP320C6211BGFNA100 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSOR |

| TMP320C6211BGGP100 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSOR |

| TMP320C6211BGGPA100 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSOR |

| TMP320C6211BGHK100 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSOR |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。