- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384010 > TLV5580PW (Texas Instruments, Inc.) 8-BIT, 80 MSPS LOW-POWER A/D CONVERTER PDF資料下載

參數(shù)資料

| 型號(hào): | TLV5580PW |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | 8-BIT, 80 MSPS LOW-POWER A/D CONVERTER |

| 中文描述: | 8位,80 MSPS的低功耗A / D轉(zhuǎn)換器 |

| 文件頁(yè)數(shù): | 16/34頁(yè) |

| 文件大?。?/td> | 531K |

| 代理商: | TLV5580PW |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)當(dāng)前第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)

TLV5580

8-BIT, 80 MSPS LOW-POWER A/D CONVERTER

SLAS205A – DECEMBER 1998 – REVISED JANUARY 1999

16

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

PRINCIPLE OF OPERATION

reference terminals

The voltages on terminals REFBI and REFTI determine the TLV5580’s input range. Since the device has an

internal voltage reference generator with outputs available on REFBO respectively REFTO, corresponding

terminals can be directly connected externally to provide a contained ADC solution. Especially at higher

sampling rates, it is advantageous to have a wider analog input range. The wider analog input range is

achievable by using external voltage references (e.g., at AVDD = 3.3 V, the full scale range can be extended

from 1 Vpp (internal reference) to 1.3 Vpp (external reference) as shown in Table 1). These voltages should not

be derived via a voltage divider from a power supply source. Instead, use a bandgap-derived voltage reference

to derive both references via an opamp circuit. Refer to the schematic of the TLV5580 evaluation module for

an example circuit.

When using external references, the full-scale ADC input range and its dc position can be adjusted. The

full-scale ADC range is always equal to V

REFT

– V

REFB

. The maximum full-scale range is dependent on AV

DD

as shown in the specification section. In addition to the limitation on their difference, V

REFT

and V

REFB

each also

have limits on their useful range. These limits are also dependent on AV

DD

.

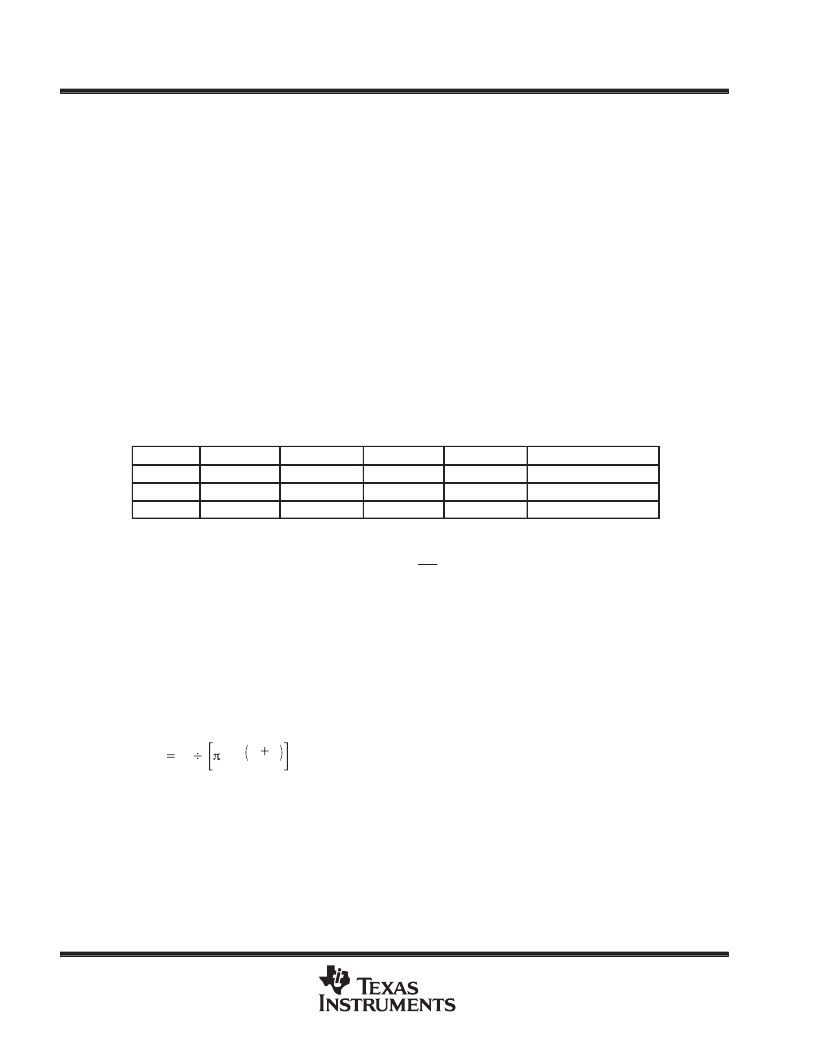

Table 3 summarizes these limits for 3 cases.

Table 1. Recommended Operating Modes

AVDD

3 V

VREFB(min)

0.8 V

VREFB(max)

1.2 V

VREFT(min)

1.8 V

VREFT(max)

2.2 V

[VREFT–VREFB]max

1 V

3.3 V

0.8 V

1.2 V

2.1 V

2.5 V

1.3 V

3.6 V

0.8 V

1.2 V

2.4 V

2.8 V

1.6 V

digital inputs

The digital inputs are CLK, STDBY, PWDN_REF, and OE. All these signals, except CLK, have an internal

pull-down resistor to connect to digital ground. This provides a default active operation mode using internal

references when left unconnected.

The CLK signal at high frequencies should be considered as an analog input. Overshoot/undershoot should be

minimized by proper termination of the signal close to the TLV5580. An important cause of performance

degradation for a high-speed ADC is clock jitter. Clock jitter causes uncertainty in the sampling instant of the

ADC, in addition to the inherent uncertainty on the sampling instant caused by the part itself, as specified by

its aperture jitter. There is a theoretical relationship between the frequency (f) and resolution (2

N

) of a signal

that needs to be sampled and the maximum amount of aperture error dt

max

that is tolerable. The following

formula shows the relation:

dtmax

1

f 2N

1

As an example, for an 8–bit converter with a 15-MHz input, the jitter needs to be kept <41 pF in order not to have

changes in the LSB of the ADC output due to the total aperture error.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV5592 | 2-BIT ANALOG-TO-DIGITAL CONVERTER FOR FLEX PAGER CHIPSET |

| TLV5592D | 2-BIT ANALOG-TO-DIGITAL CONVERTER FOR FLEX PAGER CHIPSET |

| TLV5604D | 2.7-V TO 5.5-V 10-BIT 3-mS QUADRUPLE DIGITAL-TO-ANALOG CONVERTERS WITH POWER DOWN |

| TLV5604PW | 2.7-V TO 5.5-V 10-BIT 3-mS QUADRUPLE DIGITAL-TO-ANALOG CONVERTERS WITH POWER DOWN |

| TLV5606D | 2.7 V TO 5.5 V LOW POWER 10-BIT DIGITAL-TO-ANALOG CONVERTERS WITH POWER DOWN |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV5590 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:2-BIT ANALOG-TO-DIGITAL CONVERTER FOR FLEX |

| TLV5590ED | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TLV5590EDR | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TLV5590EPWR | 制造商:Texas Instruments 功能描述: |

| TLV5591 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:SEMICONDUCTOR SIGNAL PROCESSOR |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。