- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98253 > TLV320AIC26IRHBRG4 (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQCC32 PDF資料下載

參數(shù)資料

| 型號(hào): | TLV320AIC26IRHBRG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQCC32 |

| 封裝: | 5 X 5 MM, GREEN, PLASTIC, QFN-32 |

| 文件頁(yè)數(shù): | 32/67頁(yè) |

| 文件大?。?/td> | 883K |

| 代理商: | TLV320AIC26IRHBRG4 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)當(dāng)前第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)

TLV320AIC26

SLAS412 DECEMBER 2003

www.ti.com

38

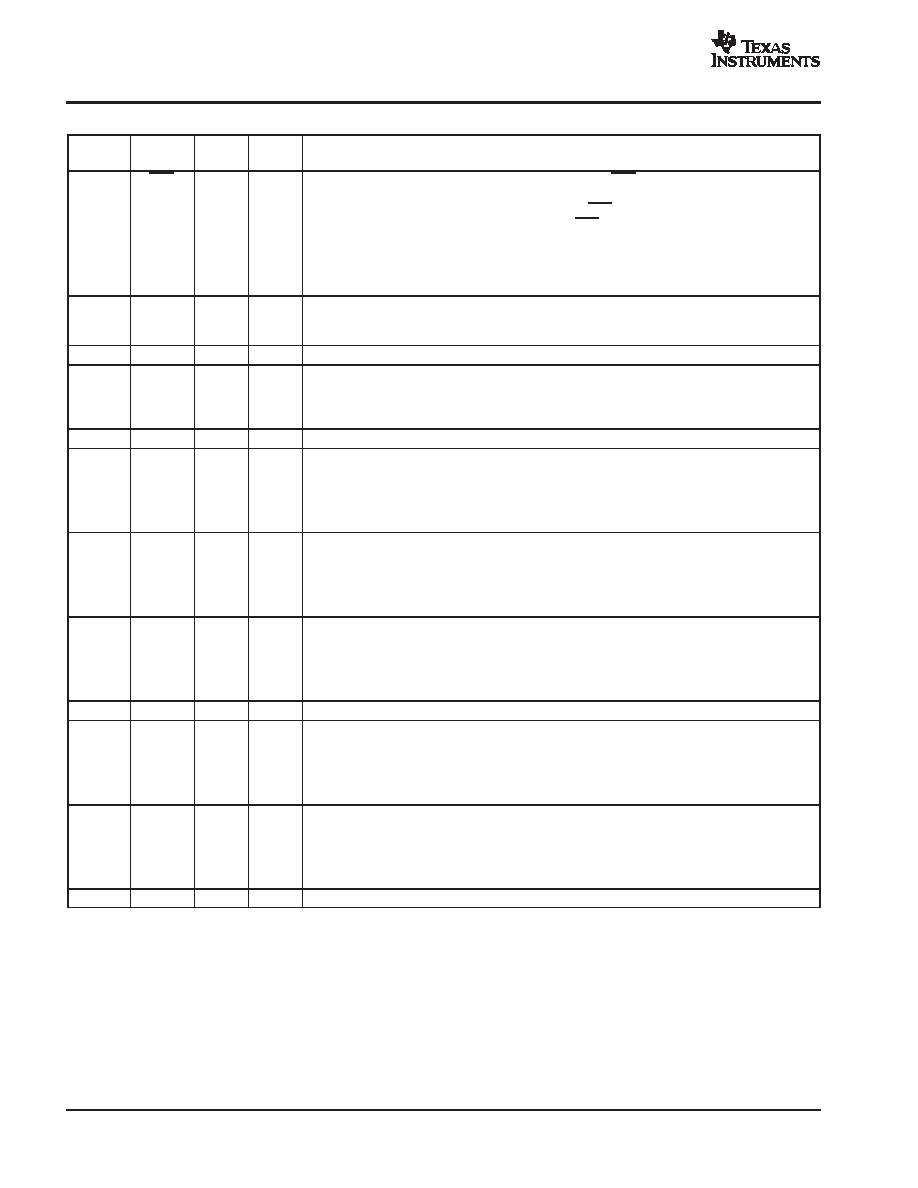

REGISTER 01H: Status Register

BIT

NAME

READ/

WRITE

RESET

VALUE

FUNCTION

D15D14

DAV

R/W

10

Data Available. These two bits program the function of the DAV pin.

00 => Reserved

01 => Acts as data available (Active Low) only. The DAV goes low as soon as one set of ADC

conversion is completed. For scan mode, DAV remains low as long as all the appropriate

registers have not been read out.

10 => Reserved

11 => Reserved

Note: D15D14 should be programmed to 01 for the ’AIC26 to operate correctly.

D13

PWRDN

R

0

AUXADC Power down status

0 => AUXADC is active

1 => AUXADC stops conversion and powers down

D12

R

0

Reserved

D11

DAVAIL

R

0

Data Available Status

0 => No data available.

1 => Data is available(i.e., one set of conversion is done).

Note: This bit is cleared only after all the converted data has been completely read out.

D10D7

R

0000

Reserved

D6

B1STAT

R

0

BAT1 Data Register Status

0 => No new data is available in BAT1 data register

1 => New data is available in BAT1 data register

Note: This bit is cleared only after the converted data of BAT1 has been completely read out of the

register.

D5

B2STAT

R

0

BAT2 Data Register Status

0 => No new data is available in BAT2 data register

1 => New data is available in BAT2 data register

Note: This bit is cleared only after the converted data of BAT2 has been completely read out of the

register.

D4

AXSTAT

R

0

AUX Data Register Status

0 => No new data is available in AUX data register

1 => New data is available in AUX data register

Note: This bit is cleared only after the converted data of AUX has been completely read out of the

register.

D3

R

0

Reserved

D2

T1STAT

R

0

TEMP1 Data Register Status

0 => No new data is available in TEMP1 data register

1 => New data is available in TEMP1 data register

Note: This bit is cleared only after the converted data of TEMP1 has been completely read out of the

register.

D1

T2STAT

R

0

TEMP2 Data Register Status

0 => No new data is available in TEMP2 data register

1 => New data is available in TEMP2 data register

Note: This bit is cleared only after the converted data of TEMP2 has been completely read out of the

register.

D0

R

0

Reserved

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV320AIC27CPFB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TLV320AIC27IPFB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TLV320AIC27TPFB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TLV320AIC28IRGZR | SPECIALTY CONSUMER CIRCUIT, PQCC48 |

| TLV320AIC28IRGZ | SPECIALTY CONSUMER CIRCUIT, PQCC48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV320AIC27 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:STEREO AUDIO CODEC |

| TLV320AIC27CPFB | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

| TLV320AIC27IPFB | 制造商:TI 制造商全稱:Texas Instruments 功能描述:STEREO AUDIO CODEC |

| TLV320AIC27PFB | 制造商:TI 制造商全稱:Texas Instruments 功能描述:STEREO AUDIO CODEC |

| TLV320AIC27TPFB | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。