- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373652 > TLC157M (Electronic Theatre Controls, Inc.) EPROM/ROM-Based 8-Bit Microcontroller Series PDF資料下載

參數(shù)資料

| 型號(hào): | TLC157M |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | EPROM/ROM-Based 8-Bit Microcontroller Series |

| 中文描述: | 存儲(chǔ)器/基于ROM的8位微控制器系列 |

| 文件頁(yè)數(shù): | 10/50頁(yè) |

| 文件大小: | 552K |

| 代理商: | TLC157M |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)

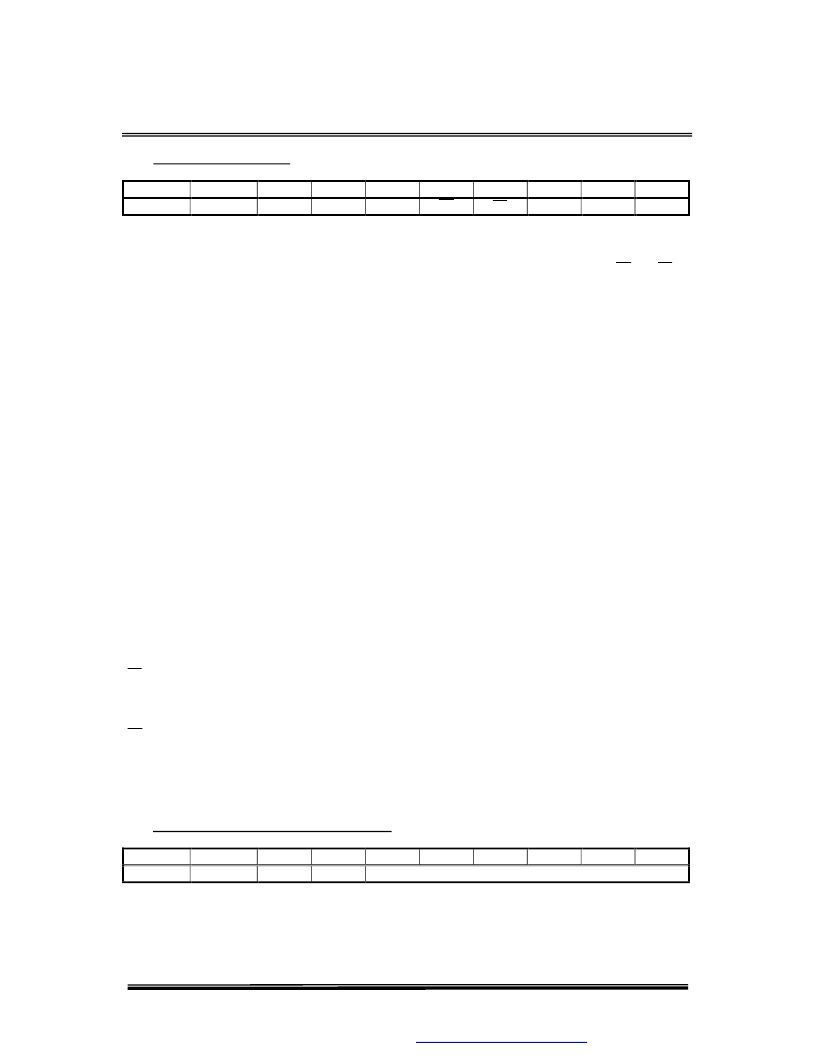

2.1.4 STATUS (Status Register)

Address

Name

03h (r/w)

STATUS

This register contains the arithmetic status of the ALU, the RESET status.

If the STATUS Register is the destination for an instruction that affects the Z, DC or C bits, then the write to these

three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the

TO

and

PD

bits

are not writable. Therefore, the result of an instruction with the STATUS Register as destination may be different

than intended. For example, CLRR STATUS will clear the upper three bits and set the Z bit. This leaves the

STATUS Register as 000u u1uu (where u = unchanged).

C

: Carry/borrow bit.

ADDAR, ADDIA

= 1, a carry occurred.

= 0, a carry did not occur.

SUBAR, SUBIA

= 1, a borrow did not occur.

= 0, a borrow occurred.

Note : A subtraction is executed by adding the two’s complement of the second operand. For rotate (RRR, RLR)

instructions, this bit is loaded with either the high or low order bit of the source register.

DC

: Half carry/half borrow bit.

ADDAR, ADDIA

= 1, a carry from the 4th low order bit of the result occurred.

= 0, a carry from the 4th low order bit of the result did not occur.

SUBAR, SUBIA

= 1, a borrow from the 4th low order bit of the result did not occur.

= 0, a borrow from the 4th low order bit of the result occurred.

Z

:

Zero bit.

= 1, the result of a logic operation is zero.

= 0, the result of a logic operation is not zero.

PD

: Power down flag bit.

= 1, after power-up or by the CLRWDT instruction.

= 0, by the SLEEP instruction.

TO

: Time overflow flag bit.

= 1, after power-up or by the CLRWDT or SLEEP instruction.

= 0, a watch-dog time overflow occurred.

GP2:GP0

: General purpose read/write bits.

2.1.5 FSR (Indirect Data Memory Address Pointer)

Address

Name

B7

B6

B5

04h (r/w)

FSR

RP1

RP0

Bit5:Bit0

: Select registers address in the indirect addressing mode. See 2.1.1 for detail description.

RP1:RP0

: For TLC154/155/156, these bits are not used. Read as “1”s.

For TLC157, these bits are used to switching the bank of four data memory banks. See 2.1.1 for

detail description.

B7

GP2

B6

GP1

B5

GP0

B4

TO

B3

PD

B2

Z

B1

DC

B0

C

B4

Indirect data memory address pointer

B3

B2

B1

B0

TLC

TLC156

Rev0.95 Nov 20, 2003

P.2/TLC156

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLC157P | EPROM/ROM-Based 8-Bit Microcontroller Series |

| TLC157R | EPROM/ROM-Based 8-Bit Microcontroller Series |

| TLC154ED | EPROM/ROM-Based 8-Bit Microcontroller Series |

| TLC226A | SENSITIVE GATE TRIACS |

| TLC116 | SENSITIVE GATE TRIACS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLC157P | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EPROM/ROM-Based 8-Bit Microcontroller Series |

| TLC157R | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EPROM/ROM-Based 8-Bit Microcontroller Series |

| TLC16C550BIPT | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel 制造商:Texas Instruments 功能描述: |

| TLC193 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DUAL MICROPOWER LinCMOSE VOLTAGE COMPARATOR |

| TLC193D | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DUAL MICROPOWER LinCMOSE VOLTAGE COMPARATOR |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。