- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361500 > TK75018DCTL (TOKO INC) SWITCHED CAPACITOR VOLTAGE CONVERTER WITH REGULATOR PDF資料下載

參數(shù)資料

| 型號: | TK75018DCTL |

| 廠商: | TOKO INC |

| 元件分類: | 穩(wěn)壓器 |

| 英文描述: | SWITCHED CAPACITOR VOLTAGE CONVERTER WITH REGULATOR |

| 中文描述: | SWITCHED CAPACITOR CONVERTER, 35 kHz SWITCHING FREQ-MAX, PDIP8 |

| 封裝: | DIP-8 |

| 文件頁數(shù): | 7/8頁 |

| 文件大小: | 91K |

| 代理商: | TK75018DCTL |

May 1999 TOKO, Inc.

Page 7

TK75018

PIN DESCRIPTIONS (CONT.)

INPUT CAPACITOR CHARGING PINS (CAP

+

/CAP

-

)

The positive driving pin of C

IN

(CAP +) charges the positive

node of the capacitor to V

IN

during t

CH

and pulls it down to

ground during t

DIS

. The negative driving pin of C

IN

(CAP -) pulls the negative node of the capacitor to ground

during t

CH

and is driven into the output during t

DIS

.

CIRCUIT GROUND (GND)

All potentials are referenced to this ground unless otherwise

noted.

OUTPUT VOLTAGE (V

OUT

)

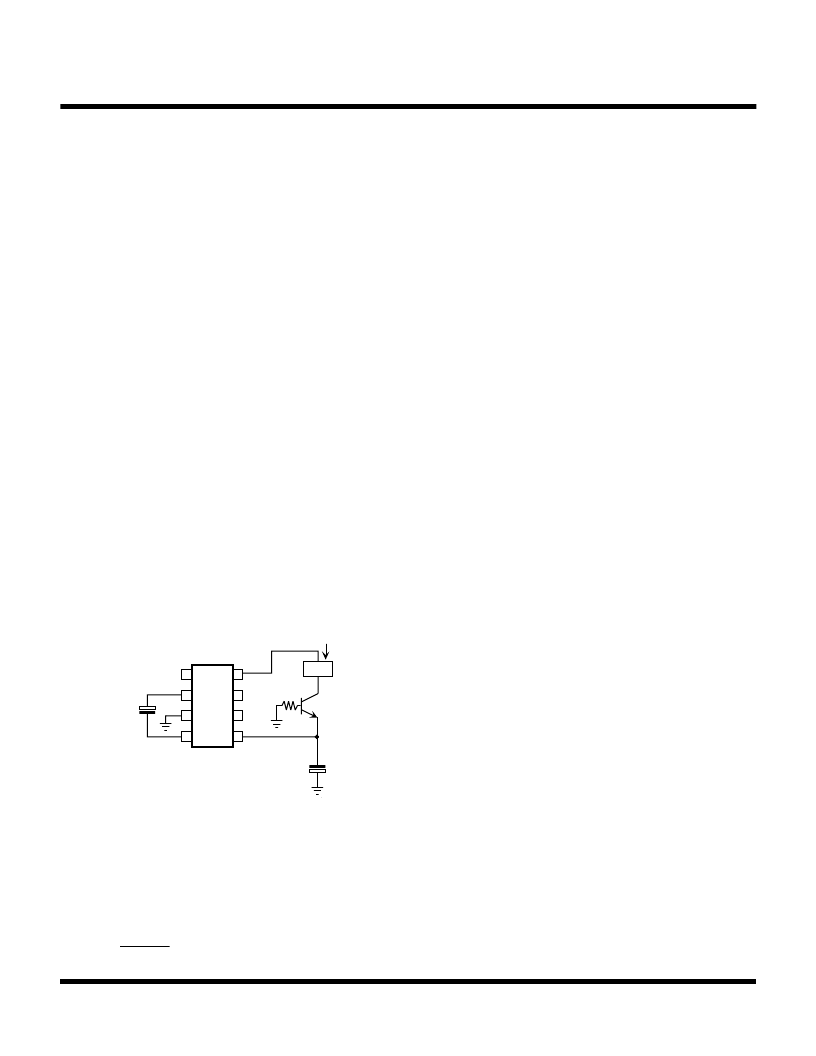

In most applications, a capacitor must be placed from this

pin to ground to integrate the charge pulses delivered by

C

IN

. A minimum of ten times C

IN

is recommended. Since

the output voltage serves as the substrate inside the IC,

the design must ensure that this pin is never raised to a

higher potential than ground. This phenomenon will tend to

occur when a positive-supply-to-negative-supply load is

present at the converter output. A circuit, such as the one

shown in Figure 4, is recommended. Under normal

operation, the transistor will appear as a short circuit. But

the sink current will be cut off from the output pin if the

voltage starts to approach ground. The resistor is chosen

to keep the transistor saturated under all steady-state

operating conditions.

The equation below can be used to calculate the values of

the feedback resistors (R1 and R2) needed to achieve a

desired output voltage.

R

2

= R

1

+1 where R

1

≥

24 k

(

1.2 V

)

|V

|

CIN

+

+

LOAD

COUT

V+

IL

CAP +

GND

CAP -

V +

VOUT

REFERENCE VOLTAGE (V

ref

)

This pin provides a nominal 2.5 V buffered reference for

external use. Normal output current should be kept below

~160

μ

A.

OSCILLATOR PROGRAMMING (OSC)

This pin can be used to alter the nominal 25 kHz frequency

of the internal oscillator. An internal timing capacitor of

~150 pF is alternately charged during t

CH

and discharged

during t

DIS

with a 7

μ

A current source to fixed threshold

levels. Adding an external capacitor from the OSC pin to

ground will parallel the 150 pF capacitor to slow down the

clock period. Adding a small external capacitor from the

OSC pin to the CAP

+

pin will source/sink extra charge into/

out-of the internal timing capacitor to speed up the transition

between thresholds and thereby raise the oscillator

frequency. It is recommended that, in the latter

configuration, the capacitor be kept below ~30 pF.

Synchronization of multiple TK75018s can be accomplished

by adding pull-up resistors from the OSC pin to the

reference voltage and using an open collector from an

NPN transistor to provide the discharge. The NPN is then

driven by a clocking pulse, and the same pulse can be

used to drive multiple devices in the same configuration.

It is not recommended to pull the OSC pin high with a low-

impedance source. To synchronize and regulate with

multiple devices, an external reference can be used as the

reference point for the error voltage divider, thus allowing

the internal reference to be used as the pull-up point for the

OSC pin.

INPUT VOLTAGE (V

+

)

The input voltage is used to charge C

IN

during the time t

CH

during each clock period. C

IN

is then discharged into the

output capacitor during time t

DIS

. During t

CH

, the input

current will be approximately 2.2 times the output current.

During t

DIS

, the input current will be approximately 0.2

times the output current. A low ESR bypass capacitor will

average out the varying current seen by the input supply -

yielding an average input current of approximately 1.1

times the output current. The bypass capacitor should be

placed as near to the TK75018 as possible to disallow

inductive spikes on the supply rail of the IC. A minimum of

2

μ

F is recommended.

FIGURE 4: POSITIVE REFERENCED LOAD

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TK75018 | SWITCHED CAPACITOR VOLTAGE CONVERTER WITH REGULATOR |

| TK75018MCTL | SWITCHED CAPACITOR VOLTAGE CONVERTER WITH REGULATOR |

| TK75018VCTL | SWITCHED CAPACITOR VOLTAGE CONVERTER WITH REGULATOR |

| TK75020 | ZVS RESONANT CONTROLLER |

| TK75020TL | ZVS RESONANT CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TK75018MCTL | 制造商:TOKO 制造商全稱:TOKO, Inc 功能描述:SWITCHED CAPACITOR VOLTAGE CONVERTER WITH REGULATOR |

| TK75018VCTL | 制造商:TOKO 制造商全稱:TOKO, Inc 功能描述:SWITCHED CAPACITOR VOLTAGE CONVERTER WITH REGULATOR |

| TK75020 | 制造商:TOKO 制造商全稱:TOKO, Inc 功能描述:ZVS RESONANT CONTROLLER |

| TK75020TL | 制造商:TOKO 制造商全稱:TOKO, Inc 功能描述:ZVS RESONANT CONTROLLER |

| TK75020TL/75020 | 制造商:TOKO 制造商全稱:TOKO, Inc 功能描述:ZVS RESONANT CONTROLLER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。