- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371180 > TDA10045 (NXP Semiconductors N.V.) DVB-T channel receiver PDF資料下載

參數(shù)資料

| 型號: | TDA10045 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | DVB-T channel receiver |

| 中文描述: | DVB - T通道接收器 |

| 文件頁數(shù): | 7/20頁 |

| 文件大小: | 94K |

| 代理商: | TDA10045 |

2001 Nov 08

7

Philips Semiconductors

Product specification

DVB-T channel receiver

TDA10045H

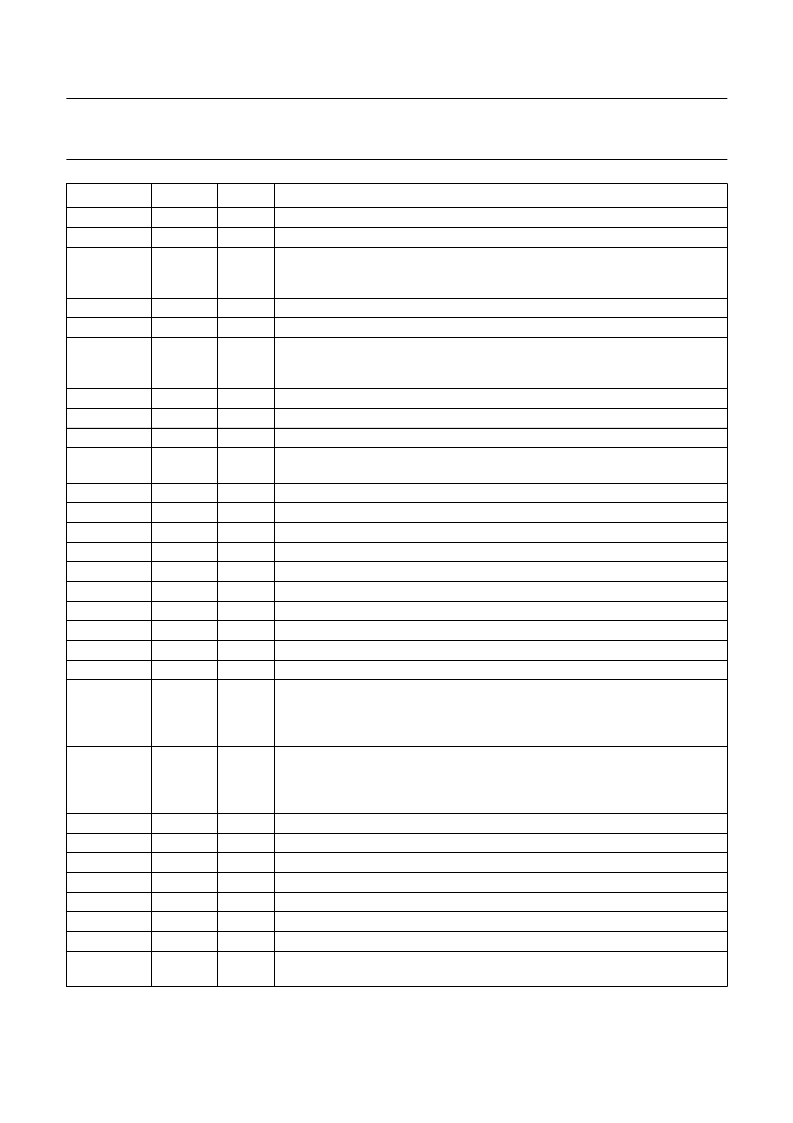

DEN

OCLK

DO[7:5]

65

66

O

O

O

output data validation signal; active HIGH during the valid and regular data bytes

output clock; OCLK is the output clock for the parallel DO[7:0] outputs

output data carrying the current sample of the current MPEG2 packet

(188 bytes), delivered on the rising edge of OCLK by default when the serial

mode is selected. The output data is delivered by DO[0].

digital supply voltage for the core (1.8 V typ.)

digital ground supply (0 V)

output data carrying the current sample of the current MPEG2 packet

(188 bytes), delivered on the rising edge of OCLK by default when the serial

mode is selected. The output data is delivered by DO[0].

digital supply voltage for the pads (3.3 V typ.)

digital ground supply (0 V)

crystal oscillator input pin

crystal oscillator output pin; typically a fundamental crystal oscillator is

connected between pins XIN and XOUT

digital supply voltage for the core (1.8 V typ.)

digital ground supply (0 V)

not connected

power supply input for the digital circuits of the PLL module (1.8 V typ.)

ground return for the digital circuits of the PLL module

not connected

ground return for the analog circuits of the PLL module

power supply input for the analog circuits of the PLL module (3.3 V typ.)

ground return for the analog circuits

power supply input for the analog circuits; the DC voltage should be 3.3 V

positive input to the ADC; this pin is DC biased to half supply through an internal

resistor divider (2

×

20 k

resistors). In order to remain in the range of the ADC,

the voltage difference between pins V

IP

and V

IM

should be between

0.5 and

+0.5 V.

negative input to the ADC; this pin is DC biased to half supply to remain in the

range of the ADC, the voltage difference between pins V

IP

and V

IM

should be

between

0.5 and +0.5 V through an internal resistor divider (2

×

20 k

resistors)

negative reference voltage for the ADC

positive reference voltage for the ADC

power supply input for the analog circuits; the DC voltage should be 3.3 V

ground return for analog circuits

ground return for the analog clock drivers

power supply input for the analog clock drivers; the DC voltage should be 3.3 V

ground return for the digital switching circuitry

power supply input for the digital switching circuitry; sensitive to the supply

noise; the DC voltage should be 1.8 V

67 to 69

V

DDD18

V

SSD

DO[4:0]

70

71

O

72 to 76

V

DDD33

V

SSD

XIN

XOUT

77

78

79

80

I

(2)

O

V

DDD18

V

SSD

n.c.

V

CCD(PLL)

DGND

n.c.

PPLGND

V

CCA(PLL)

V

SSA3

V

DDA3

V

IP

81

82

83

84

85

86

87

88

89

90

91

V

IM

92

V

ref(neg)

V

ref(pos)

V

DDA3

V

SSA3

V

SSA2

V

DDA2

V

SSA1

V

DDD1

93

94

95

96

97

98

99

100

SYMBOL

PIN

TYPE

DESCRIPTION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TDA10045H | DVB-T channel receiver |

| TDA1005A | FREQUENCY MULTIPLEX PLL STEREO DECODER |

| TDA1005AT | FREQUENCY MULTIPLEX PLL STEREO DECODER |

| TDA10085 | Single chip DVB-S/DSS channel receiver |

| TDA10085HT | Single chip DVB-S/DSS channel receiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TDA10045H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:DVB-T channel receiver |

| TDA10046AHT/C1,518 | 制造商:Trident Microsystems, Ltd. 功能描述:TTMTDA10046AHT/C1,518 HYBRID SILICON TUN |

| TDA10046HT | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Single-chip DVB-T channel |

| TDA10048HC/C200,557 | 制造商:NXP Semiconductors 功能描述:PHATDA10048HC/C200.557 REEL |

| TDA10048HN/C200,51 | 制造商:Entropic Communications 功能描述:TDA10048HN/HVQFN48/REEL13DP//C |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。