- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385914 > TCM320AC37N (Texas Instruments, Inc.) VOICE-BAND AUDIO PROCESSORS VBAPE PDF資料下載

參數(shù)資料

| 型號: | TCM320AC37N |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | VOICE-BAND AUDIO PROCESSORS VBAPE |

| 中文描述: | 語音頻帶音頻處理器VBAPE |

| 文件頁數(shù): | 14/23頁 |

| 文件大小: | 317K |

| 代理商: | TCM320AC37N |

TCM320AC36, TCM320AC37

VOICE-BAND AUDIO PROCESSORS (VBAP

)

SLWS003C – MAY 1992 – REVISED APRIL – 1998

14

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

PRINCIPLES OF OPERATION

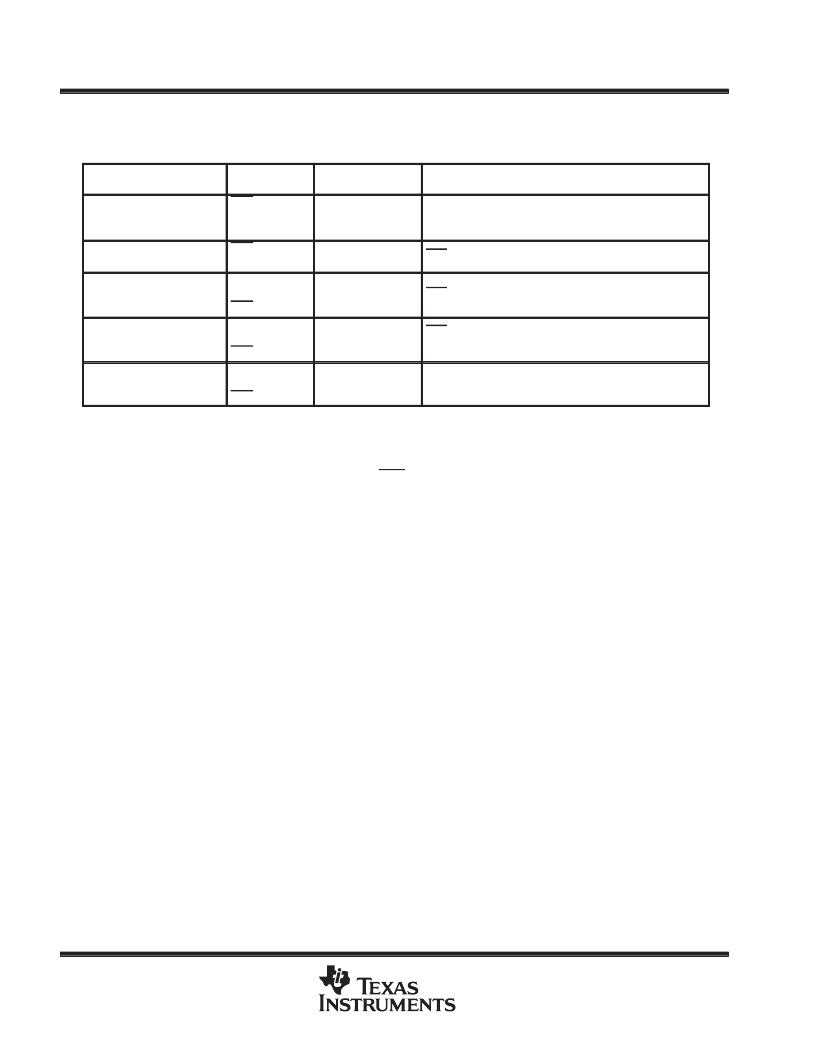

Table 1. Power-Down and Standby Procedures

DEVICE STATUS

PROCEDURE

TYPICAL POWER

CONSUMPTION

DIGITAL OUTPUT STATUS

Power on

PDN = high,

FSX = pulses,

FSR = pulses

40 mW

Digital outputs active but not loaded

Power down

PDN = low,

FSX, FSR = X

FSX = low,

FSR = low,

PDN = high

FSX = low,

FSR = pulses,

PDN = high

FSR = low,

FSX = pulses,

PDN = high

3 mW

TSX and DOUT in the high-impedance state

Entire device on standby

mode

5 mW

TSX and DOUT in the high-impedance state

Only transmit channel in

standby mode

20 mW

TSX and DOUT in the high-impedance state within five

frames

Only receive channel in

standby mode

20 mW

Digital outputs active but not loaded

X = don’t care

fixed-data-rate timing

Fixed-data-rate timing, selected by connecting DCLKR to V

CC

,

uses the master clock (CLK), frame

synchronization clocks (FSX and FSR), and the TSX output. FSX and FSR are inputs that set the sampling

frequency. Data is transmitted on DOUT on the positive transitions of CLK following the rising edge of FSX. Data

is received on DIN on the falling edges of CLK following FSR. A D/A conversion is performed on the received

digital word, and the resulting analog sample is held on an internal sample-and-hold capacitor until transferred

to the receive filter. The data word is eight bits long in the companded mode and 16 bits long in the linear mode.

variable-data-rate timing

Variable-data-rate timing is selected by connecting DCLKR to the receive data clock. In this mode, the master

clock (CLK) controls the switched-capacitor filters, while data transfer into DIN and out of DOUT is controlled

by DCLKR and DCLKX respectively. This allows the data to be transferred in and out of the device at any rate

up to the frequency of the master clock. DCLKR and DCLKX must be synchronous with CLK.

While the FSX input is high, data is transmitted from DOUT on consecutive positive transitions of DCLKX.

Similarly, while the FSR input is high, the data word is received at DIN on consecutive negative transitions of

DCLKR. The transmitted data word at DOUT is repeated in all remaining time slots in the frame as long as

DCLKX is pulsed and FSX is held high. This feature, which allows the data word to be transmitted more than

once per frame, is available only with variable-data-rate timing.

asynchronous operations

To avoid crosstalk problems associated with special interrupt circuits, the design includes separate converters,

filters, and voltage references on the transmit and receive sides. This allows completely independent operation

of the two channels. In either timing mode, the master clock, data clock, and time-slot strobe must be

synchronized at the beginning of each frame.

precision voltage references

A precision band-gap reference voltage is generated internally and is used to supply all the references required

for operation of both the transmit and receive channels. The gain in each channel is trimmed during the

manufacturing process. This ensures very accurate, stable gain performance over variations in supply voltage

and device temperature.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TCM320AC37PT | VOICE-BAND AUDIO PROCESSORS VBAPE |

| TCM320AC54 | MONOLITHIC SERIAL INTERFACE COMBINED PCM CODEC AND FILTER |

| TCM320AC54DW | MONOLITHIC SERIAL INTERFACE COMBINED PCM CODEC AND FILTER |

| TCM320AC54N | MONOLITHIC SERIAL INTERFACE COMBINED PCM CODEC AND FILTER |

| TCM809(中文) | 3-Pin Microcontroller Reset Monitors(3引腳微控制器復(fù)位監(jiān)控器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TCM320AC37PT | 制造商:TI 制造商全稱:Texas Instruments 功能描述:VOICE-BAND AUDIO PROCESSORS VBAPE |

| TCM320AC38 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:VOICE-BAND AUDIO PROCESSORS (VBAPE) |

| TCM320AC39CPT | 制造商:Texas Instruments 功能描述: |

| TCM320AC39IDW | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TCM320AC46 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:GEBERAL-PURPOSE AUDIO INTERFACE FOR DSP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。