- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98158 > TAS3218PZPR (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP100 PDF資料下載

參數(shù)資料

| 型號: | TAS3218PZPR |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封裝: | GREEN, PLASTIC, TQFP-100 |

| 文件頁數(shù): | 18/79頁 |

| 文件大?。?/td> | 1263K |

| 代理商: | TAS3218PZPR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁

Control Pins

RESET

www.ti.com ....................................................................................................................................................................................................... SLES235 – JULY 2008

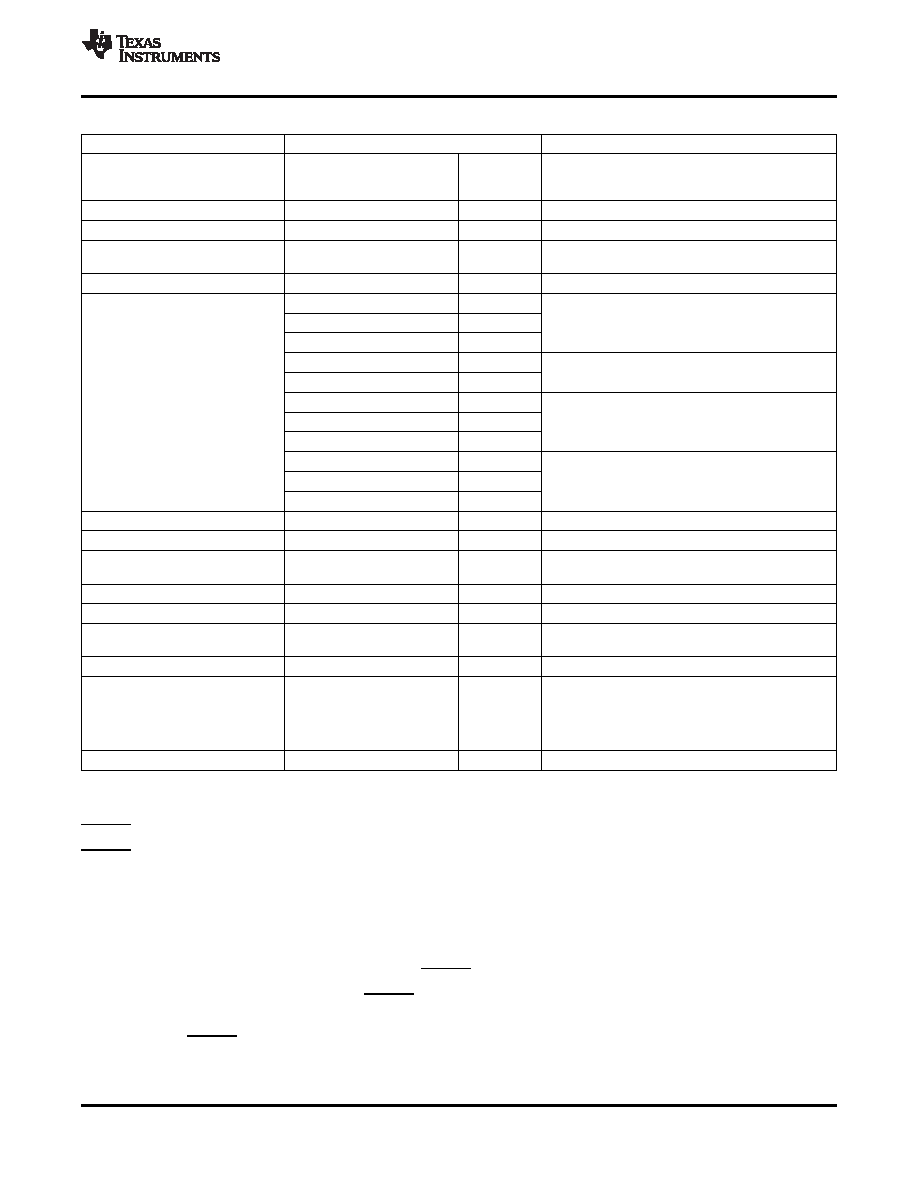

Table 4. Process Description

PROCESS STATE

ESFR

DESCRIPTION

DSP idle

uP initialization

I2C bus high

uP Flush Internal RAM

Clear micro internal RAM (256 byte)

uP Flush External RAM

Clear micro external RAM (2048 byte)

uP command to Flush Delay

clr_dly_ram (0xc0 bit(3))

1

Memory

uP initialize variables

Initialize variables

mute0_t

0

mute1_t

0

Default mutez control

mute2_t

0

reset_dac_mod

0xff

reset_adc_sinc

0x03

uP set default H/W configuration

clock_control1

0x0a

clock_delay_control2

0x05

clock_delay_sel

0x80

i2s_word_byte

0x22

IW/OW: 24 bit

i2c_mode_byte

0x22

IM/OM: I2S

sap_en

1

uP Flush uP Instruction RAM

mem_sel

0x02

Clear uP Instruction RAM (16384Byte)

uP Flush DSP Instruction RAM

mem_sel

0x01

Clear DSP Instruction RAM (3328W)

Clear DSP lower coefficient RAM (1024 W) and data

uP flush DSP lower coef/data RAM

mem_sel

0x00

(48 bit) RAM (768 W)

Enable I2C master I/F

Setup I2C master I/F mode (enable interrupt 10)

EEPROM load

Disable I2C master mode and

i2c_ms_ctl

0

Switch control MUX to slave I2C port

enable slave I/F

Switch ROM to RAM

pc_source

1

If (gpio_in_3_0 == 1) {

Host_dsp = 1; /* keep DSP turned off */

Load default DSP

host_dsp

0

} else {

Program and coefficient

Host_dsp = 0; /* turn on DSP */

}

GPIO1 output low

Enable GPIO output mode, and output low.

RESET is an asynchronous control signal that restores all TAS3218 components to the default configuration.

When a reset occurs, the Digital Audio Processor (DAP) is put into an idle state and the M8051 MCU starts

initialization. A reset can be initiated by inputting logic 0 on the reset pin . A reset will also be issued at power up

sequencing by the internal 1.8V regulator power sub-system.

NOTE:

There is a 1.3-s de-glitch filter on the RESET pin.

During a power up sequencing process, RESET should be held low until the DVDD and AVDD power inputs

have reached a voltage of 3.0 V.

As long as the RESET pin is held a logic 0 the device is in the reset state. During this reset state, all I2C and

Serial Data bus operations are ignored. The I2C interface SCL and SDA lines goes HIGH and remain in that state

until device initialization has completed.

Copyright 2008, Texas Instruments Incorporated

25

Product Folder Link(s): TAS3218

相關PDF資料 |

PDF描述 |

|---|---|

| TAS3218PZP | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TAS5000PFB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TAS5000PFBG4 | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TAS5001PFB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TAS5001IPFBR | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TAS-3225A | 制造商:TEW 功能描述: |

| TAS-3225A 44.000KHZ | 制造商:TEW 功能描述: |

| TAS-3225J 13.56MHz }20ppm/22pF | 制造商:Tokyo Denpa 功能描述:13.560000MHz }20ppm }15ppm 22pF 3.2~2.5~0.55mm +85 -30 3.2mm 2.5mm 0.55mm Cut Tape |

| TAS-3225J 14.7456MHz }20ppm/18pF | 制造商:Tokyo Denpa 功能描述:14.745600MHz }20ppm }15ppm 18pF 3.2~2.5~0.55mm +85 -30 3.2mm 2.5mm 0.55mm Cut Tape |

| TAS-3225J 16MHz }20ppm/16pF | 制造商:Tokyo Denpa 功能描述:16.000000MHz }20ppm }15ppm 16pF 3.2~2.5~0.55mm +85 -30 3.2mm 2.5mm 0.55mm Cut Tape |

發(fā)布緊急采購,3分鐘左右您將得到回復。