- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383840 > STA003 MPEG 2.5 LAYER III AUDIO DECODER PDF資料下載

參數(shù)資料

| 型號: | STA003 |

| 英文描述: | MPEG 2.5 LAYER III AUDIO DECODER |

| 中文描述: | 2.5第三層的MPEG音頻解碼器 |

| 文件頁數(shù): | 21/32頁 |

| 文件大?。?/td> | 299K |

| 代理商: | STA003 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

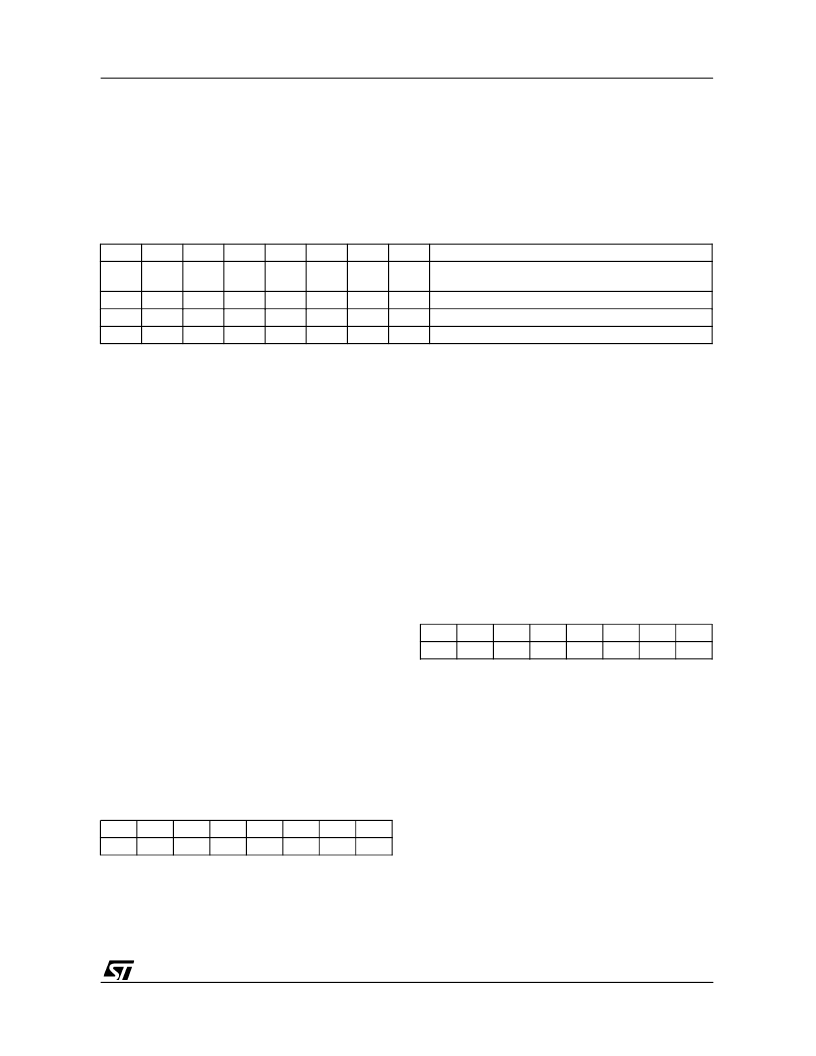

PCMCROSS

Address: 0x56

Type: R/W

Software Reset: 0x00

Hardware Reset: 0x00

MSB

b7

X

LSB

b0

0

b6

X

b5

X

b4

X

b3

X

b2

X

b1

0

Description

Left channel is mapped on the left output.

Right channel is mapped on the Right output

Left channel is duplicated on both Output channels.

Right channel is duplicated on both Output channels

Right and Left channels are toggled

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

0

1

1

1

0

1

The default configuration for this register is ’0x00’.

ANCILLARY DATA BUFFER

Address: 0x59 - 0x5D

Type: RO

Software Reset: 0x00

Hardware Reset: 0x00

STA003T can extract max 56 bytes/MPEG frame.

To know the number of A.D. bits available every

MPEG frame, the ANCCOUNT_L and ANC-

COUNT_H registers (0x41 and 0x42) have to be

read.

The buffer dimension is 5 bytes, written by

STA003T core in sequential order. The timing in-

formation to read the buffer can be obtained by

reading the FRAME_CNT registers (0x67 - 0x69).

To fill up the buffer with a new 5-bytes slot, the

STA003T waits until a CMD_INTERRUPT regis-

ter is written by the master.

MFSDF (X)

Address: 0x61

Type: R/W

Software Reset: 0x0F

Hardware Reset: 0x0F

MSB

b7

X

The register contains the values for PLL X divider

(see Fig. 6).

LSB

b0

M0

b6

X

b5

X

b4

M4

b3

M3

b2

M2

b1

M1

The value is changed by the internal STA003T

Core, to set the clock frequencies, according to

the incoming bitstream. This value can be even

set by the user to select the PCM interface con-

figuration.

The VCO output frequency is divided by (X+1).

DAC_CLK_MODE

Address: 0x63

Type: RW

Software Reset: 0x00

Hardware Reset: 0x00

MSB

b7

X

This register is used to select the operating mode

for OCLK clock signal.

If it is set to ’1’, the OCLK frequency is fixed, and

it is mantained to the value fixed by the user even

if the sampling frequency of the incoming bit-

stream changes.

If the MODE flag is set to ’0’, the OCLK frequency

changes, and can be set to (512, 384, 256) * Fs.

The default configuration for this mode is 256 *

Fs.

When this mode is selected, the default OCLK

frequency is 12.288 MHz.

LSB

b0

MODE

b6

X

b5

X

b4

X

b3

X

b2

X

b1

X

STA003T

21/32

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| STA10 | ASIC |

| STA351A | General Purpose Sink Driver Array |

| STA352A | General Purpose Source Driver Array |

| STA474A | H-bridge Motor Driver Array |

| STB100NF03L-03T4 | TRANSISTOR | MOSFET | N-CHANNEL | 30V V(BR)DSS | 100A I(D) | TO-263AB |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| STA003T | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:MPEG 2.5 LAYER III AUDIO DECODER |

| STA011 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:L-band RF front-end for digital radio |

| STA011E | 制造商:ST 功能描述:DAB |

| STA013 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:MPEG 2.5 LAYER III AUDIO DECODER |

| STA013 | 功能描述:音頻 DSP MPEG Audio Decoder RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風格: 封裝 / 箱體: 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復。