- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372295 > ST24LW21M6TR (意法半導(dǎo)體) 1 Kbit x8 Dual Mode Serial EEPROM for VESA PLUG & PLAY PDF資料下載

參數(shù)資料

| 型號: | ST24LW21M6TR |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | 1 Kbit x8 Dual Mode Serial EEPROM for VESA PLUG & PLAY |

| 中文描述: | 1千位x8雙模式串行EEPROM的韋莎插頭 |

| 文件頁數(shù): | 3/22頁 |

| 文件大小: | 159K |

| 代理商: | ST24LW21M6TR |

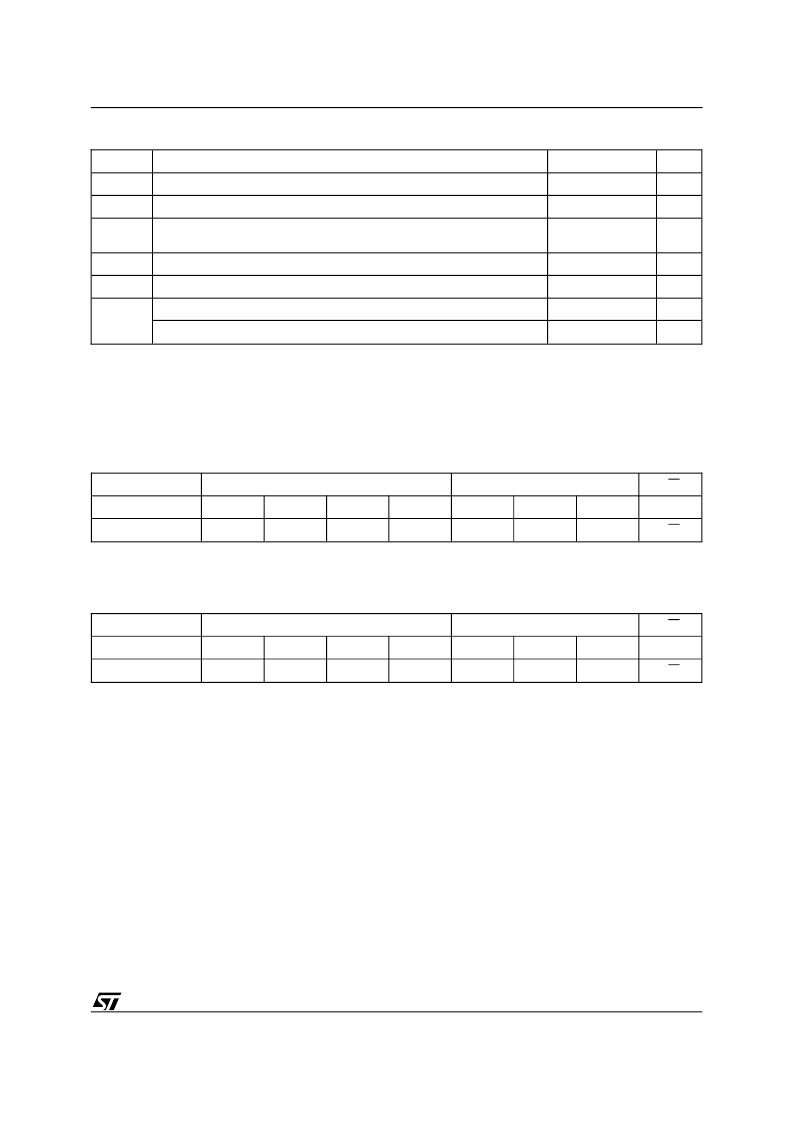

Symbol

Parameter

Value

Unit

T

A

Ambient Operating Temperature

–40 to 85

°

C

T

STG

Storage Temperature

–65 to 150

°

C

T

LEAD

Lead Temperature, Soldering

(SO8 package)

(PSDIP8 package)

40 sec

10 sec

215

260

°

C

V

IO

Input or Output Voltages

–0.3 to 6.5

V

V

CC

Supply Voltage

–0.3 to 6.5

V

V

ESD

Electrostatic Discharge Voltage (Human Body model)

(2)

4000

V

Electrostatic Discharge Voltage (Machine model)

(3)

500

V

Notes:

1. Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Ratings"

may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other

conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum

Rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other

relevant quality documents.

2. MIL-STD-883C, 3015.7 (100pF, 1500

).

3. EIAJ IC-121 (Condition C) (200pF, 0

).

Table 2. Absolute Maximum Ratings

(1)

Device Code

Chip Enable

RW

Bit

b7

b6

b5

b4

b3

b2

b1

b0

Device Select

1

0

1

0

X

X

X

RW

Note:

The MSB b7 is sent first.

X = 0 or 1.

Table 3A. Device Select Code (ST24LC21B, ST24LW21, ST24FC21 and ST24FW21)

The ST24xy21 can operate in two modes: Trans-

mit-Only mode and I

2

C bidirectional mode. When

powered, the device is in Transmit-Only mode with

EEPROM data clocked out from the rising edge of

the signal applied on VCLK.

The device will switch to the I

2

C bidirectional mode

upon the falling edge of the signal applied on SCL

pin. When in I

2

C mode, the ST24LC21B (or the

ST24LW21) cannot switch back to the Transmit

Only mode (except when the power supply is re-

moved). For the ST24FC21, ST24FC21B (or the

ST24FW21), after the falling edge of SCL, the

memory enter in a transition state which allowed to

switch back to the Transmit-Only mode if no valid

I

2

C activity is observed. Both Plastic Dual-in-Line

and Plastic Small Outline packages are available.

Transmit Only Mode

After a Power-up, the ST24xy21 is in the Transmit

Only mode. A proper initialization sequence (see

Figure 3) must supply nine clock pulses on the

VCLK pin (in order to internally synchronize the

device). During this initialization sequence, the

SDA pin is in high impedance. On the rising edge

of the tenth pulse applied on VCLK pin, the device

will output the first bit of byte located at address 00h

(most significant bit first).

DESCRIPTION

(cont’d)

Device Code

Chip Enable

RW

Bit

b7

b6

b5

b4

b3

b2

b1

b0

Device Select

1

0

1

0

0

0

0

RW

Note:

The MSB b7 is sent first.

X = 0 or 1.

Table 3B. Device Select Code (ST24FC21B)

3/22

ST24LC21B, ST24LW21, ST24FC21, ST24FC21B, ST24FW21

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST25C16M3 | Cyclone II FPGA 5K FBGA-256 |

| ST25C16M6 | Cyclone II FPGA 20K FBGA-484 |

| ST25C16ML1 | IC APEX 20KE FPGA 100K 240-PQFP |

| ST25C16ML3 | Cyclone II FPGA 5K PQFP-208 |

| ST25C16ML6 | Cyclone FPGA 4K FBGA-324 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST24T1M5ZBE | 功能描述:SWITCH TOGGLE MINI UNSELD RoHS:是 類別:開關(guān) >> 撥動開關(guān) 系列:ST 標(biāo)準(zhǔn)包裝:1 系列:A 電路:雙刀雙擲 開關(guān)功能:開-開-開 觸點額定電壓:6A @ 125VAC 觸動器類型:扁平型 觸動器長度:11.38mm 發(fā)光:不發(fā)光 安裝類型:面板安裝 端接類型:焊片 軸襯螺紋:1/4-40 包裝:散裝 |

| ST24T3H 032397 | 制造商:Comair Rotron 功能描述:FAN 80MM 24VDC |

| ST24T3H | 制造商:Comair Rotron 功能描述:FAN 80MM 24VDC |

| ST24W01 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:SERIAL 1K 128 x 8 EEPROM |

| ST24W01B1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:I2C Serial EEPROM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。