- 您現在的位置:買賣IC網 > PDF目錄98142 > SST85LD1004T-60-RI-LBTE (SILICON STORAGE TECHNOLOGY INC) IDE COMPATIBLE, FLASH MEMORY DRIVE CONTROLLER, PBGA91 PDF資料下載

參數資料

| 型號: | SST85LD1004T-60-RI-LBTE |

| 廠商: | SILICON STORAGE TECHNOLOGY INC |

| 元件分類: | 存儲控制器/管理單元 |

| 英文描述: | IDE COMPATIBLE, FLASH MEMORY DRIVE CONTROLLER, PBGA91 |

| 封裝: | 12 X 24 MM, ROHS COMPLIANT, MO-210, LBGA-91 |

| 文件頁數: | 7/11頁 |

| 文件大?。?/td> | 204K |

| 代理商: | SST85LD1004T-60-RI-LBTE |

Fact Sheet

4 GByte NANDrive

SST85LD1004T

2008 Silicon Storage Technology, Inc.

S71394(01)-00-000

09/08

5

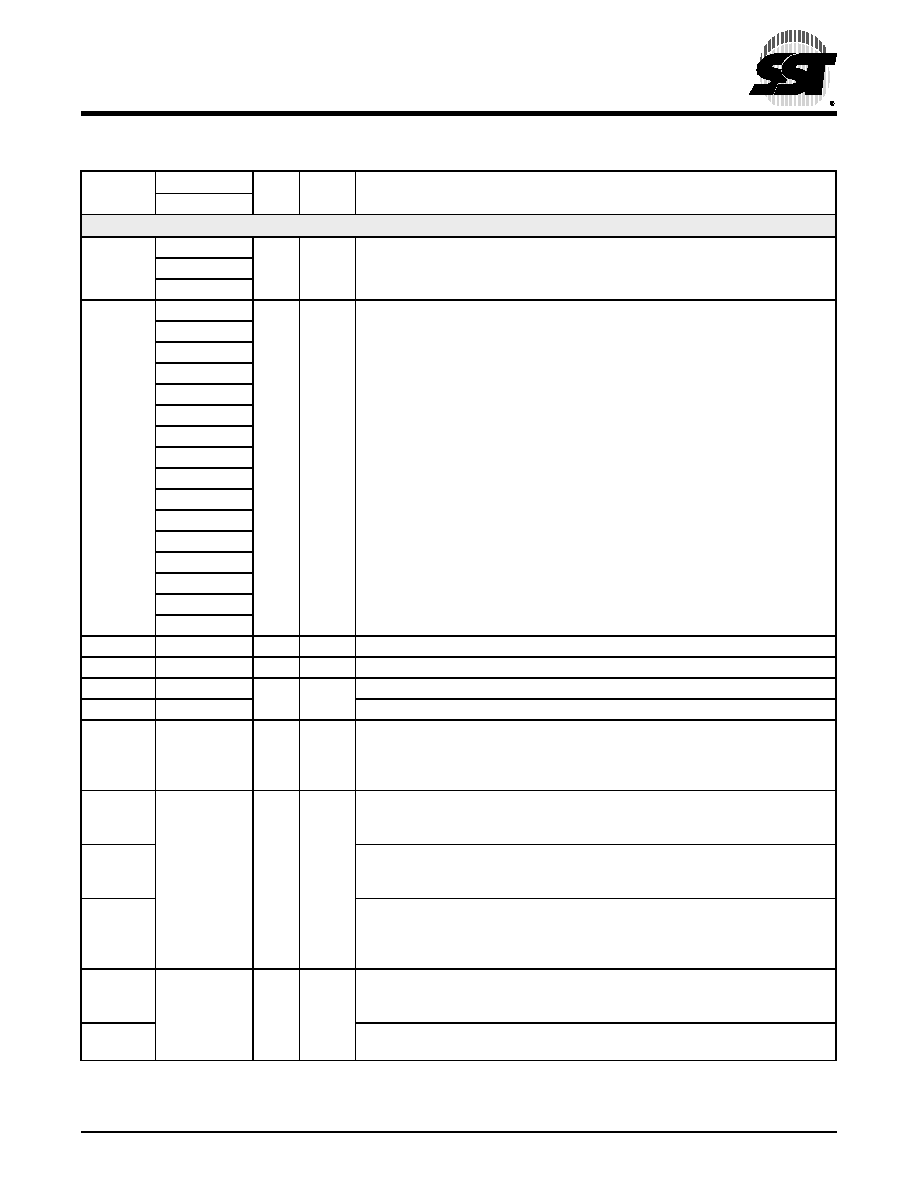

TABLE

3-1: Pin Assignments (1 of 2)

Symbol

Pin No.

Pin

Type

I/O

Type

Name and Functions

91-LBGA

Host Side Interface

A2

K8

I

I1Z

A[2:0] are used to select one of eight registers in the Task File.

A1

K3

A0

L2

D15

H8

I/O

I1Z/O2 D[15:0] Data bus

D14

G9

D13

G8

D12

H7

D11

F9

D10

F8

D9

E8

D8

F7

D7

F4

D6

H4

D5

E3

D4

H3

D3

F3

D2

G3

D1

F2

D0

G2

DMACK#

K2

I

I2U

DMA Acknowledge - input from host

DMARQ

J3

O

O1

DMA Request to host

CS1FX#

L3

II2Z

CS1FX# is the chip select for the task file registers

CS3FX#

L8

CS3FX# is used to select the alternate status register and the Device Control register.

CSEL

L9

I

I1U

This internally pulled-up signal is used to configure this device as a Master or a Slave.

When this pin is grounded, this device is configured as a Master. When the pin is open,

this device is configured as a Slave. The pin setting should remain the same from

Power-on to Power-down.

IORD#

H2

I

I2Z

IORD#: This is an I/O Read Strobe generated by the host. When

Ultra DMA mode is not active, this signal gates I/O data from the

device.

HDMARDY#

HDMARDY#: In Ultra DMA mode when DMA Read is active, this signal is asserted by

the host to indicate that the host is ready to receive Ultra DMA data-in bursts. The host

may negate HDMARDY# to pause an Ultra DMA transfer.

HSTROBE

HSTROBE: When DMA Write is active, this signal is the data-out strobe generated by

the host. Both the rising and falling edges of HSTROBE cause data to be latched by the

device. The host may stop generating HSTROBE edges to pause an Ultra DMA data-

out burst.

IOWR#

H9

I

I2Z

This is an I/O Write Strobe generated by the host. When Ultra

DMA mode is not active, this signal is used to clock I/O data into

the device.

STOP

When Ultra DMA mode protocol is active, the assertion of this signal causes the termi-

nation of the Ultra DMA burst

相關PDF資料 |

PDF描述 |

|---|---|

| SST85LD1008M-60-PC-LBTE | IDE COMPATIBLE, FLASH MEMORY DRIVE CONTROLLER, PBGA91 |

| SST85LD1008M-60-PC-LBTE | IDE COMPATIBLE, FLASH MEMORY DRIVE CONTROLLER, PBGA91 |

| SST85LP1004A-M-C-LBTE | IDE COMPATIBLE, FLASH MEMORY DRIVE CONTROLLER, PBGA91 |

| SST85LP1004A-M-C-LBTE | IDE COMPATIBLE, FLASH MEMORY DRIVE CONTROLLER, PBGA91 |

| SST85LP1004B-M-C-LFTE | IDE COMPATIBLE, FLASH MEMORY DRIVE CONTROLLER, PBGA91 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| SST85LD1004T-60-RI-LCTE | 功能描述:閃存 4G NAND 60ns 3.3V Industrial RoHS:否 制造商:ON Semiconductor 數據總線寬度:1 bit 存儲類型:Flash 存儲容量:2 MB 結構:256 K x 8 定時類型: 接口類型:SPI 訪問時間: 電源電壓-最大:3.6 V 電源電壓-最小:2.3 V 最大工作電流:15 mA 工作溫度:- 40 C to + 85 C 安裝風格:SMD/SMT 封裝 / 箱體: 封裝:Reel |

| SST85LD1004T-60-RI-LCTE-TM023 | 功能描述:閃存 4G NAND 60ns 3.3V Industrial RoHS:否 制造商:ON Semiconductor 數據總線寬度:1 bit 存儲類型:Flash 存儲容量:2 MB 結構:256 K x 8 定時類型: 接口類型:SPI 訪問時間: 電源電壓-最大:3.6 V 電源電壓-最小:2.3 V 最大工作電流:15 mA 工作溫度:- 40 C to + 85 C 安裝風格:SMD/SMT 封裝 / 箱體: 封裝:Reel |

| SST85LD1004U-60-5I-LBTE | 功能描述:閃存 4G NAND 60ns 3.3V Industrial RoHS:否 制造商:ON Semiconductor 數據總線寬度:1 bit 存儲類型:Flash 存儲容量:2 MB 結構:256 K x 8 定時類型: 接口類型:SPI 訪問時間: 電源電壓-最大:3.6 V 電源電壓-最小:2.3 V 最大工作電流:15 mA 工作溫度:- 40 C to + 85 C 安裝風格:SMD/SMT 封裝 / 箱體: 封裝:Reel |

| SST85LD1008M-60-4C-LBTE | 功能描述:閃存 8G NAND 60ns 3.3V Commercial RoHS:否 制造商:ON Semiconductor 數據總線寬度:1 bit 存儲類型:Flash 存儲容量:2 MB 結構:256 K x 8 定時類型: 接口類型:SPI 訪問時間: 電源電壓-最大:3.6 V 電源電壓-最小:2.3 V 最大工作電流:15 mA 工作溫度:- 40 C to + 85 C 安裝風格:SMD/SMT 封裝 / 箱體: 封裝:Reel |

| SST85LD1008M-60-PC-LBTE | 功能描述:閃存 8GB NAND 60ns 3.3V Commercial RoHS:否 制造商:ON Semiconductor 數據總線寬度:1 bit 存儲類型:Flash 存儲容量:2 MB 結構:256 K x 8 定時類型: 接口類型:SPI 訪問時間: 電源電壓-最大:3.6 V 電源電壓-最小:2.3 V 最大工作電流:15 mA 工作溫度:- 40 C to + 85 C 安裝風格:SMD/SMT 封裝 / 箱體: 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。