- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98142 > SST55LC100-45-C-BWE FLASH MEMORY DRIVE CONTROLLER, PBGA84 PDF資料下載

參數(shù)資料

| 型號: | SST55LC100-45-C-BWE |

| 元件分類: | 存儲控制器/管理單元 |

| 英文描述: | FLASH MEMORY DRIVE CONTROLLER, PBGA84 |

| 封裝: | ROHS COMPLIANT, MO-210, TFBGA-84 |

| 文件頁數(shù): | 19/80頁 |

| 文件大小: | 758K |

| 代理商: | SST55LC100-45-C-BWE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

26

Advance Information

CompactFlash Card Controller

SST55LC100

2005 Silicon Storage Technology, Inc.

S71298-00-000

10/05

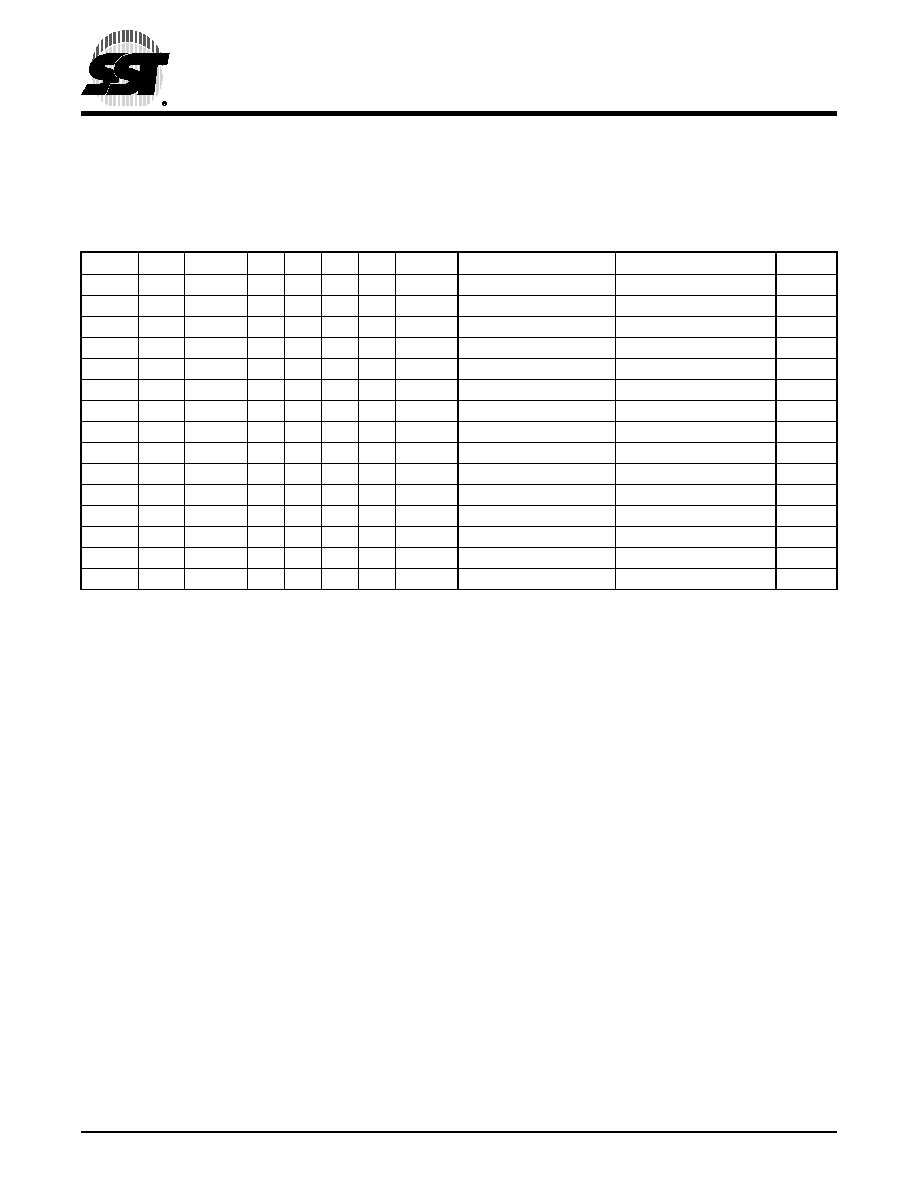

9.1.3 Memory Mapped Addressing

When the CompactFlash card registers are accessed via memory references, the registers appear in the common

memory space window: 0-2 KByte as follows:

TABLE

9-4: MEMORY MAPPED DECODING

REG#

A10

A9-A4

A3

A2

A1

A0

Offset

OE#=0

WE#=0

Notes

1

0

X

0

Even RD Data

Even WR Data

1,2

1. Register 0 is accessed with CE1# low and CE2# low as a word register on the combined Odd Data Bus and Even Data Bus (D15-

D0). This register may also be accessed by a pair of byte accesses to the offset 0 with CE1# low and CE2# high. Note that the

address space of this word register overlaps the address space of the Error and Feature byte-wide registers that lie at offset 1. When

accessed twice as byte register with CE1# low, the first byte to be accessed is the Even Byte of the word and the second byte

accessed is the Odd Byte of the equivalent word access.

A byte access to address 0 with CE1# high and CE2# low accesses the error (read) or feature (write) register.

2. Registers at offset 8, 9 and D are non-overlapping duplicates of the registers at offset 0 and 1.

Register 8 is equivalent to register 0, while register 9 accesses the Odd Byte. Therefore, if the registers are byte accessed in the

order 9 then 8 the data will be transferred Odd Byte then Even Byte.

Repeated byte accesses to register 8 or 0 will access consecutive (Even then Odd) Bytes from the data buffer. Repeated word

accesses to register 8, 9 or 0 will access consecutive words from the data buffer. Repeated byte accesses to register 9 are not sup-

ported. However, repeated alternating byte accesses to registers 8 then 9 will access consecutive (Even then Odd) Bytes from the

data buffer. Byte accesses to register 9 access only the Odd Byte of the data.

1

0

X

0

1

Error

Features

1

0

X

0

1

0

2

Sector Count

1

0

X

0

1

3

Sector No.

1

0

X

0

1

0

4

Cylinder Low

1

0

X

0

1

0

1

5

Cylinder High

1

0

X

0

1

0

6

Select Card/Head

1

0

X

0

1

7

Status

Command

1

0

X

1

0

8

Dup. Even RD Data

Dup. Even WR Data

1

0

X

1

0

1

9

Dup. Odd RD Data

Dup. Odd WR Data

1

0

X

1

0

1

D

Dup. Error

Dup. Features

1

0

X

1

0

E

Alt Status

Device Ctl

1

0

X

1

F

Drive Address

Reserved

1

X

0

8

Even RD Data

Even WR Data

3

3. Accesses to even addresses between 400H and 7FFH access register 8. Accesses to odd addresses between 400H and 7FFH

access register 9. This 1 KByte memory window to the data register is provided so that hosts can perform memory to memory block

moves to the data register when the register lies in memory space.

Some hosts, such as the X86 processors, must increment both the source and destination addresses when executing the memory to

memory block move instruction. Some PCMCIA socket adapters also have auto incrementing address logic embedded within them.

This address window allows these hosts and adapters to function efficiently.

Note that this entire window accesses the Data register FIFO and does not allow random access to the data buffer within the

CompactFlash card. A word access to address at offset 8 will provide even data on the low-order byte of the data bus, along with odd

data at offset 9 on the high-order byte of the data bus.

1

X

1

9

Odd RD Data

Odd WR Data

T9-4.0 1298

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SST55LC100M-45-C-BWE | IDE COMPATIBLE, FLASH MEMORY DRIVE CONTROLLER, PBGA84 |

| SST55LD017D-40-C-TQWE | FLASH MEMORY DRIVE CONTROLLER, PQFP100 |

| SST55LD017D-40-I-TQW | FLASH MEMORY DRIVE CONTROLLER, PQFP100 |

| SST55LD019A-45-C-TQPE | FLASH MEMORY DRIVE CONTROLLER, PQFP64 |

| SST55LD019C-45-I-BWE | FLASH MEMORY DRIVE CONTROLLER, PBGA84 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SST55LC100-45-C-TQWE | 功能描述:總線收發(fā)器 Compact Flash Card Controller RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SST55LC100-45-I-BWE | 制造商:SST 制造商全稱:Silicon Storage Technology, Inc 功能描述:CompactFlash Card Controller |

| SST55LC100-45-I-TQWE | 制造商:SST 制造商全稱:Silicon Storage Technology, Inc 功能描述:CompactFlash Card Controller |

| SST55LC100M | 制造商:SST 制造商全稱:Silicon Storage Technology, Inc 功能描述:CompactFlash Card Controller |

| SST55LC100M-45-C-BWE | 功能描述:總線收發(fā)器 Compact Flash 45MHz 3.3V Commercial RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。